# Aligned Carbon Nanotube Synaptic Transistors for Large-Scale Neuromorphic **Computing**

Ivan Sanchez Esqueda,\*\*,†© Xiaodong Yan,‡ Chris Rutherglen,§ Alex Kane,§ Tyler Cain,§ Phil Marsh,§ Qingzhou Liu,‡ Kosmas Galatsis,\*,§ Han Wang,\*,‡© and Chongwu Zhou\*,‡©

<sup>†</sup>Information Sciences Institute, University of Southern California, Marina del Rey, California 90292, United States

ABSTRACT: This paper presents aligned carbon nanotube (CNT) synaptic transistors for large-scale neuromorphic computing systems. The synaptic behavior of these devices is achieved via charge-trapping effects, commonly observed in carbon-based nanoelectronics. In this work, charge trapping in the high-k dielectric layer of top-gated CNT field-effect transistors (FETs) enables the gradual analog programmability of the CNT channel conductance with a large dynamic range (i.e., large on/off ratio). Aligned CNT synaptic devices present significant improvements over conventional memristor technologies (e.g., RRAM), which suffer from abrupt transitions in the conductance

modulation and/or a small dynamic range. Here, we demonstrate exceptional uniformity of aligned CNT FET synaptic behavior, as well as significant robustness and nonvolatility via pulsed experiments, establishing their suitability for neural network implementations. Additionally, this technology is based on a wafer-level technique for constructing highly aligned arrays of CNTs with high semiconducting purity and is fully CMOS compatible, ensuring the practicality of largescale CNT+CMOS neuromorphic systems. We also demonstrate fine-tunability of the aligned CNT synaptic behavior and discuss its application to adaptive online learning schemes and to homeostatic regulation of artificial neuron firing rates. We simulate the implementation of unsupervised learning for pattern recognition using a spike-timing-dependentplasticity scheme, indicate system-level performance (as indicated by the recognition accuracy), and demonstrate improvements in the learning rate resulting from tuning the synaptic characteristics of aligned CNT devices.

KEYWORDS: carbon nanotube, synapse, transistor, neuromorphic, machine learning

he approaching fundamental limits for process scaling of complementary metal-oxide-semiconductor (CMOS) technology have led to significant material and device research aimed at developing a more efficient and better performing replacement for MOS field-effect-transistors (MOSFETs).<sup>1-4</sup> Low-dimensional (e.g., 2-D and 1-D) materials such as graphene and carbon nanotubes (CNTs) are promising candidates with excellent scalability and desirable electronic transport properties under low-voltage operation.<sup>5–9</sup> Moreover, recent developments in the functionality of CNT devices, 10-13 as well as their compatibility with three-dimensional (3-D) integration, 14,15 may enable the implementation of non-von-Neumann architectures that eliminate the separation of memory and logic, thus reducing power consumption and heat generation resulting from expensive data transferring (i.e., the von-Neumann "bottleneck"). 16,17 The time- and power-efficient computing benefits

of these architectures are especially beneficial for low-power mobile electronic systems. Moreover, the increasing deployment of mobile, data-gathering devices for the Internet of Things (IoT) presents a significant need for efficient and highthroughput data preprocessing at the edge of the network (i.e., edge computing). 18,19

Neuromorphic architectures, inspired by the human brain, emulate the structure and functionality of biological neural systems and can enable the realization of highly efficient computing systems.<sup>20,21</sup> By utilizing the synaptic properties of resistive switching (i.e., memristive) devices, artificial neural networks can be fabricated in a crossbar configuration offering the desired density, parallelism, and 3-D integration compat-

Received: May 21, 2018 Accepted: June 26, 2018 Published: June 26, 2018

Downloaded via UNIV OF SOUTHERN CALIFORNIA on July 23, 2018 at 20:31:29 (UTC). See https://pubs.acs.org/sharingguidelines for options on how to legitimately share published articles.

<sup>\*</sup>Ming Hsieh Department of Electrical Engineering, University of Southern California, Los Angeles, California 90089, United States

<sup>§</sup>Carbonics Inc., Culver City, California 90230, United States

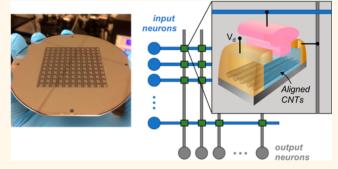

Figure 1. (a) Aligned CNT FET wafer fabricated by Carbonics. (b) Top-gated aligned CNT FET test structures (inset is the zoomed-in view of the channel region from a 10-finger device; each channel "finger" is 20  $\mu$ m wide). (c) Scanning electron microscope (SEM) image of the aligned CNT FET active region. (d) SEM of the aligned CNT channel. (e) Cross-sectional schematic of the aligned CNT FET. (f) Top view of the aligned CNT FET including t-shaped top-gate and self-aligned source/drain regions. (g) Conceptual back-end-of-line (BEOL) integration of aligned CNT FETs for artificial neural network implementation in crossbar configuration.

ibility desired for the efficient hardware implementation of machine learning algorithms and neuro-inspired computing architectures. This approach has been used to demonstrate tasks such as recognition, classification, learning, and decision making.  $^{18,25-28}$

The most widely studied memristive device for the hardware implementation of artificial neural networks in a crossbar configuration is the filamentary type (e.g., RRAM).<sup>29-33</sup> This technology offers great features including a simple twoterminal structure, low-power operation, and good endurance and retention.<sup>33</sup> However, it suffers from significant device-todevice and cycle-to-cycle variability, <sup>34</sup> as well as from abruptness of resistance modulation, <sup>35–38</sup> due to the inherent filamentary operation.<sup>39</sup> This abruptness is undesirable for neuromorphic systems<sup>40</sup> and can be eliminated from the characterization of RRAM synaptic behavior through the application of a forming step (i.e., initial generation of the conductive filament). Nonetheless, the dynamic range (i.e., resistance modulation range) after the formation of the conductive filament is limited, as further changes in resistance result only from modulation of the filament cross-sectional area. 41 Moreover, the requirement of a forming step and the significant variation of the forming/set voltage 42,43 introduce additional system-level complexity (and associated cost), unwanted for the efficient hardware implementation of artificial neural networks. Because of these limitations, synaptic devices with alternative resistive switching mechanisms are desirable. Recently, charge-trapping synaptic transistors have been proposed as an alternative for the hardware implementation of artificial neural networks. Devices with Si<sup>44</sup> as well as random network CNT channels<sup>11,12</sup> have been demonstrated with promising preliminary results. It is well established that CNT-based devices have exceptional scaling properties that extend beyond the Si roadmap<sup>8</sup> and are considered a primary candidate for next-generation computing systems that vertically integrate logic and memory. 15,45 Importantly, achieving superior device uniformity and stability requires controlled

placement of CNTs (i.e., alignment) as well as controlled semiconducting purity. 46 In this work, we present a wafer-scale aligned CNT synaptic transistor technology for large-scale neuromorphic systems. An advantage of CNTs for the development of charge-trapping synaptic transistors is their large sensitivity to charged defect scattering. Because of their small physical dimensions, CNT conductivity can change significantly as a result of changes in the charge state of nearby defects. 47,48 As we will show, the sensitivity of individual CNTs translates into measurable changes of CNT FET conductance, especially for FETs with aligned CNTs where transport and scattering effects are isolated to 1-D, 49 resulting in a robust synaptic behavior with large dynamic range. We present a thorough analysis of the robust synaptic behavior in aligned CNT transistors based on DC and pulsed electrical characterization. We discuss the implementation of aligned CNT-based artificial neural networks and present system-level simulations of unsupervised learning for pattern recognition applications. Additionally, we demonstrate the synaptic tuning capability of an aligned CNT FET and discuss its application to adaptive learning schemes for artificial neural networks and/or to implement homeostatic regulation of neuron firing rates.

# RESULTS AND DISCUSSION

Aligned CNT Synaptic Transistors. Single-walled carbon nanotubes (SWCNTs) and SWCNT FETs have exceptional 1-D electronic transport properties, making them an excellent candidate for various applications including high-speed logic devices, <sup>50</sup> radio frequency (RF) transistors, <sup>51</sup> and nonvolatile memory. <sup>52</sup> However, for most of these applications, the organized assembly (*i.e.*, alignment) of SWCNTs with controlled semiconducting purity is critical for optimizing device performance and for developing practical, reliable, and scalable technologies. <sup>46,53-55</sup> In this work, a recently improved evaporation-driven process, named floating evaporative self-assembly (FESA), <sup>56,57</sup> has been utilized by Carbonics Inc. to fabricate highly aligned SWCNT devices at the wafer level

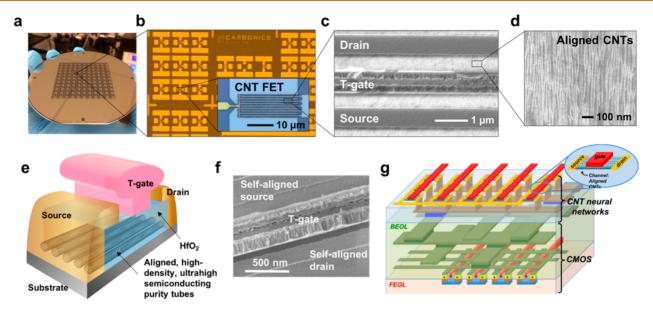

Figure 2. (a) Dual-sweep  $I_{\rm d}-V_{\rm gs}$  characteristics of aligned CNT FETs for  $V_{\rm ds}=-1.0$  and -0.05 V revealing large gate hysteresis. (b) Dependence of hysteresis window on the voltage sweep range of dual-sweep  $I_{\rm d}-V_{\rm gs}$  measurements. (c)  $I_{\rm d}-V_{\rm ds}$  characteristics for increasing  $V_{\rm gs}$ . (d) Multiple cycles of dual-sweep  $I_{\rm d}-V_{\rm gs}$  indicating repeatability of hysteresis effects. (e) Distribution of hysteresis plotted as a function of the on/off ratio. (f) Energy band diagram illustrating charge-trapping effects in aligned CNT FETs.

(Figure 1a). Figure 1b is the optical image of a multifingered top-gated aligned CNT FET. The scanning electron microscope (SEM) images of a gate region and of the aligned SWCNTs are respectively shown in Figure 1c and d. A schematic of the self-aligned T-gate transistor structure is illustrated in Figure 1e, and the SEM image of the finalized device including self-aligned source/drain regions is shown in Figure 1f. The T-gate structure is characteristic of RF application that these devices were initially designed for. It enhances gate control, helps scaling down the channel length, and reduces parasitic capacitance. Thus, it can enhance the dynamic behavior of gate-bias-dependent charge-trapping mechanisms and improve the performance of aligned CNT synaptic transistors, enabling faster operation.

This wafer-level process is fully compatible with CMOS, owing to the low-temperature fabrication of aligned CNT devices. Thus, it is feasible to achieve 3-D integration of aligned CNT devices and CMOS circuits to enable non-von-Neumann architectures, such as neuromorphic topologies, that conquer the communication bottleneck between memory and logic. Figure 1g illustrates the conceptual back-end-of-line (BEOL) 3-D integration of aligned CNT and CMOS for neuromorphic computing systems. In this architecture, aligned CNT FETs are connected in a crossbar configuration and operate as the synaptic elements of an artificial neural network, and neural circuits are implemented with CMOS. We first present the electrical characteristics of the aligned CNT FETs, followed by the demonstration and analysis of their synaptic properties. Later, we describe the aligned CNT-based neuromorphic crossbar configuration as well as the implementation and performance of artificial spiking neural networks for pattern recognition based on unsupervised learning.

Figure 2a plots the drain current  $(I_d)$  as a function of the gate-to-source voltage  $(V_{gs})$  for a drain bias  $(V_{d})$  of -1.0 V and −50 mV from a CNT FET with a channel width to length ratio of  $W/L \approx 60 \ \mu \text{m}/1 \ \mu \text{m}$ . These data are from a six-finger topgated CNT FET with 20 µm channel width per finger (only measured three of the six channels divided between two drain electrodes for a total of 60  $\mu$ m). P-type operation in the CNT FET is indicated by the exponentially increasing (negative) current with increasing  $-V_{\rm gs}$ , resulting from hole conduction in the valence band of the CNTs. The dual sweeps in Figure 2a also indicate large counterclockwise gate hysteresis attributed to a dynamic screening of the electric field due to charge injection/emission (i.e., trapping/detrapping) near and/or at the interface between the CNTs and the 4.6 nm thick HfO<sub>2</sub> gate dielectric. Figure 2b plots the dual-sweep transfer characteristics with  $V_d = -0.05$  V, measured with increasing gate sweep range from  $\pm 0.5$  to  $\pm 2.0$  V. Increasing the gate sweep range allows accessing a wider range of energetically distributed traps and enhances the field-driven tunneling mechanisms that allow charge trapping/detrapping. 59 As discussed below, this voltage control of trap occupancy allows gradually modulating charge-induced electrostatic and scattering effects, resulting in a robust synaptic device operation. For completion, in Figure 2c we plot the family of  $I_d$ - $V_{ds}$  curves obtained with increasing  $V_{\rm gs}$  from 0 V to -1.0 V in steps of -0.5 V.

We plot multiple cycles of dual-sweep  $I_{\rm d}$ – $V_{\rm gs}$  measurements from three different devices in Figure 2d, to demonstrate the repeatability of the charge-trapping effects and their impact on the hysteresis and electrical characteristics of the CNT FETs. Having a sufficiently large on/off ratio is important for achieving synaptic operation with a large dynamic range (*i.e.*, a large range of conductance modulation). We experimentally

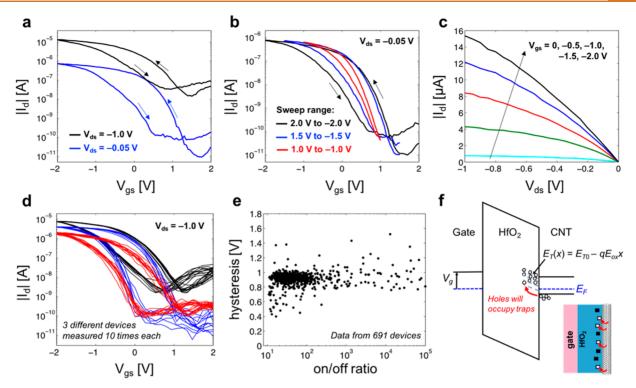

Figure 3. (a) Biasing configuration for pulsed measurements of synaptic properties of aligned CNT FETs. (b) Diagram of the pulsed measurements for long-term potentiation and long-term depression. (c) Measured synaptic characteristics of an aligned CNT FET. (d, e) Tuning the synaptic properties of aligned CNT FETs with adjustment of the potentiating/depressing voltage pulse amplitudes. (f) Reduced pulse amplitude improves linearity and stability of the synaptic response with a slight reduction in dynamic range.

verify that the aligned top-gate CNT FETs can simultaneously provide a sufficiently large on/off ratio (e.g., >10) and hysteresis window (e.g., >0.4 V) by extracting these parameters from a large set of 691 measured devices. In Figure 2e we plot the distribution, and it concentrates around an on/off ratio of ~40 and a hysteresis window of ~0.9 V, with a long tail spreading to larger on/off ratios. The tightness of the hysteresis window distribution is a good indicator of uniformity in the charge-trapping dynamics. In short-channel CNT FETs, electronic transport is quasi-ballistic (near-ballistic).<sup>60</sup> This also helps achieve a robust synaptic behavior and large dynamic range, as it enhances the sensitivity of CNT FET conductance to charged defects near the channel. When carriers can travel without being scattered by other channel impurities, Coulomb scattering induced by changes in the charge state of nearby defects can have a large impact on

In Figure 2f, the energy band diagram across the gate/HfO<sub>2</sub>/ CNT regions of the device illustrates the trapping mechanisms responsible for hysteresis and for the synaptic behavior of the aligned CNT transistors. With a negative bias applied at the gate, the energy level of near-interfacial traps in the HfO<sub>2</sub> dielectric layer will be shifted upward (due to band bending), and a fraction of them that were initially located below the Fermi level in the CNT channel  $(E_F)$  will now be located above  $E_{\rm E}$ . These traps will gradually change their occupancy, since at this biasing condition there is a large hole population in the CNT channel that can occupy the energy levels  $E_{\rm T}$  (i.e., hole trapping), resulting in a net positive change in the charge contribution due to traps. Similarly, when the gate bias is positive, the bands bend in the opposite direction, resulting in a net negative change in the trap charge contribution. We note that the trap energy distribution (relative to  $E_{\rm F}$ ) depends on bias (i.e., due to band bending) as well as position. Traps located further away from the interface see a larger shift in their energy level as a function of bias, but are also less likely to have a chance in their occupancy, as the tunneling probability of carriers from the CNT channel decreases exponentially with distance from the interface. Thus, only a fraction of near-interfacial traps having energy levels centered around  $E_{\rm F}$ , will dynamically change their charged state as a function of bias, and affect the electrostatic and transport properties of the device. In CNT FETs, traps along the surface of the dielectric but not directly in contact with the CNT (*i.e.*, surface traps) may also contribute to charging effects. The trap charge state transitions are not instantaneous and can have long-term effects that result in gate hysteresis and memory effects that are responsible for the synaptic behavior of the aligned CNT FETs.

Synaptic Properties of Aligned CNT FETs. The synaptic properties of the aligned CNT FETs are experimentally analyzed using pulsed electrical measurements. As illustrated in Figure 3a, the source terminal of the aligned CNT FETs is connected to a ground reference, while a series of gate-tosource  $(V_{gs})$  and drain-to-source  $(V_{ds})$  voltage pulses are applied to the device under test during the experiment. To characterize synaptic potentiation, a short positive  $V_{

m gs}$  pulse with amplitude  $V_{

m pot}$  and width  $t_{

m w}$  is applied as indicated in Figure 3b. Following the application of the  $V_{\rm gs}$  =  $V_{\rm pot}$  pulse, a small bias of  $V_{

m dsm}$  is applied between drain and source to measure  $I_d$  (at  $V_{gs} = 0$  V), and the process is repeated for a specified number of potentiating pulses. Similarly, synaptic depression is characterized by applying a short negative gate-tosource voltage pulse with amplitude  $V_{

m dep}$  and width  $t_{

m w}$ , followed by a small  $V_{\rm dsm}$  bias to measure  $I_{

m d}$ .

In Figure 3c we plot the synaptic characteristics of an aligned CNT FET measured with 20 potentiating and 20 depressing voltage pulses having amplitudes  $V_{\rm pot} = 2$  V and  $V_{\rm dep} = -1.4$  V, respectively, and  $t_{\rm w} = 10$   $\mu s$ . For the measurements of  $I_{\rm d}$ ,  $V_{\rm dsm} = -1.0$  V was applied for  $\sim 0.1$  s. The same device is measured 10 times (gray solid lines), and the mean is extracted (solid blue line with circles). The results in Figure 3c reveal good repeatability of the synaptic characteristics, a large dynamic range evident by >1 order of magnitude modulation of  $I_{\rm d}$ , and

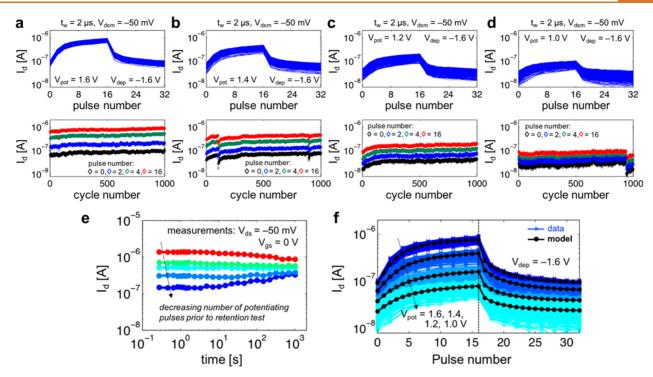

Figure 4. (a–d) Multiple cycles of synaptic properties characterized with repeated (1000) pulsed measurements. Each graph is for a different amplitude of the potentiating voltage pulse ranging from  $V_{\rm pot}=1.6$  to 1.0 V. Top:  $I_{\rm d}$  vs pulse number for all 1000 cycles; bottom: extraction of  $I_{\rm d}$  at four different levels (i.e., after four different number of pulses) vs cycle number. (e) Retention test showing samples of the programmed  $I_{\rm d}$  as a function of time immediately following the pulsed programming. (f) Collection of all data from (a)–(d) and model calculations indicating the impact of  $V_{\rm pot}$  on the abruptness and dynamic range of the aligned CNT FET conductance modulation.

good analog programmability (i.e., fine synaptic resolution). We note that each potentiating and depressing pulse is of the same amplitude and width, since previous works have used pulse trains with incremental amplitudes and/or widths to improve the synaptic response. 62,63 However, it is not clear how these incremental pre/post-synaptic pulse features can be practically implemented in neuromorphic systems. Compared to these previous works, which are mostly based on filamentary resistive-switching devices (e.g., RRAM), the aligned CNT devices have improved synaptic properties due to the inherent charge-trapping mechanisms responsible for conductance modulation. Filamentary devices generally exhibit an abrupt transition in conductance through a "forming step", during which the creation of the conductive filament is initiated. Following the creation of the conductive filamentary path, only small changes in conductance attributed to the widening of the filament are typically achieved, resulting in a limited dynamic range. In recent work, 11 it was determined that conductance modulation of ~100% in random network CNT FETs enables better performing neuromorphic system operation, compared to conventional memristors, which typically achieve <30%. Also, that CNT devices with higher semiconducting purity and isolated nanotubes may provide improvements in synaptic performance. Here, we demonstrate that in aligned CNT FETs, where transport is isolated to individual nanotubes with high semiconducting purity, we can achieve >1 order of magnitude conductance modulation, providing significant improvement over random network CNT FETs.

Charge trapping in aligned CNT FETs not only eliminates the need for a forming step but also enables gradual changes in the conductance, resulting in a robust and stable synaptic response. However, in some cases we can still observe a sharp transition after the first depressing pulse (e.g., Figure 3c). In order to eliminate this abruptness, we explore tuning of the synaptic characteristics through adjustment of the pulse amplitudes. In Figure 3d, we show independent tuning of synaptic depression based on measurements with a fixed  $V_{\rm pot}$  = 2 V and  $V_{\text{dep}} = -2.0, -1.3, \text{ and } -1.0 \text{ V (same device)}$ . We note that adjusting only  $V_{

m dep}$  results in asymmetric synaptic characteristics. It is not yet clear how this asymmetry may affect the implementation of specific neuromorphic systems or machine learning algorithms. Nevertheless, it is possible to avoid the asymmetry by simultaneously adjusting  $V_{\text{pot}}$  and  $V_{\text{dep}}$ , with a slight trade-off in dynamic range as shown in Figure 3e. Figure 3f shows the synaptic characteristics from 10 repeated measurements (gray lines) of the same device using  $V_{pot} = 1.4$ V and  $V_{\text{dep}} = -1.4 \text{ V}$  as well as the mean (solid blue line with circles). The results in Figure 3f reveal better linearity (less abruptness) in conductance modulation while maintaining a large (~1 order of magnitude) dynamic range.

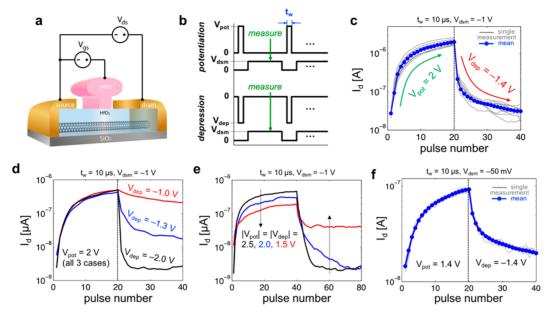

To further explore the endurance, robustness, and tuning of the synaptic properties of aligned CNT FETs, we tested a large number of potentiation/depression cycles in a single device. In Figure 4a (top) we plot  $I_{\rm d}$  measurements from 1000 consecutive synaptic characterization cycles using  $V_{\rm pot}=1.6$  V,  $V_{\rm dep}=-1.6$  V,  $t_{\rm w}=2~\mu{\rm s}$ , and  $V_{\rm dsm}=-50$  mV. From each cycle we extract  $I_{\rm d}$  after 0, 2, 4, and 16 potentiating pulses and plot them as a function of the cycle number (bottom). The results in Figure 4a illustrate the endurance and robustness of the charge-trapping-based synaptic behavior of aligned CNT FETs. For the same device, we repeat the measurement of 1000 consecutive cycles with  $V_{\rm pot}=1.4$ , 1.2, and 1.0 V, using  $V_{\rm dep}=-1.6$  V for all cases, as plotted in Figure 4b,c,d (top). Similarly, we plot the extractions of  $I_{\rm d}$  after 0, 2, 4, and 16

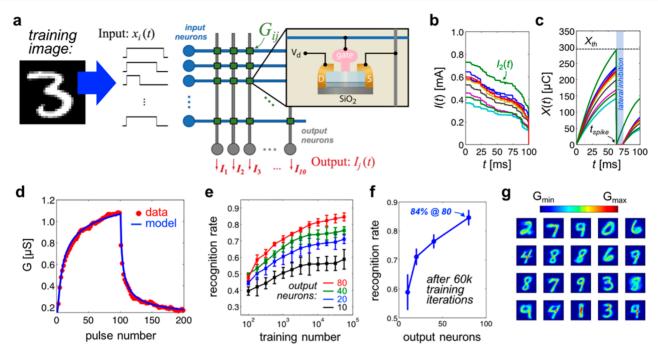

Figure 5. (a) Diagram illustrating the implementation of unsupervised learning for pattern recognition in a spiking neural network with aligned CNT synaptic devices. (b) Simulated time-dependent current in the postsynaptic (output) neurons. (c) Characteristics of output neuron potentials as simulated by an integrate and fire function, indicating the firing of the postsynaptic neuron spike as well as lateral inhibition. (d) Experimental data and model calculations of aligned CNT FET synaptic response used in the simulations of MNIST data set pattern recognition. (e) Recognition rate as a function of training number for arrays with increasing number of output neurons. (f) Recognition rate after 60 000 training cycles as a function of the number of output neurons. (g) Conductance map of 20 output neurons after training.

potentiating pulses for all cases, respectively plotted as a function of the cycle number in Figure 4b,c,d (bottom). These results verify the stability and robustness of the synaptic performance of aligned CNT FETs, as well as the precise tuning capability based on adjusting the potentiating voltage pulse amplitude.

We also verify the long-term retention of synaptic weights in aligned CNT FETs through the time-dependent sampling of  $I_d$ following the programming of various states (i.e., after various numbers of potentiating/depressing pulses). Figure 4e plots  $I_d$ vs time over approximately 4 decades of time (up to 1 ks), indicating only a small loss of the extreme states that correspond to the largest/smallest programmed channel conductance. However, in many neuromorphic computing applications and machine learning algorithm implementations, synaptic weight updating may occur at much faster rates compared to the time scale over which we measure this slight degradation in retention. Moreover, even with this reduction to the window of allowed programmed states, the dynamic range is still sufficiently large  $(\sim 3\times)$  to enable adequate synaptic weight analog programmability with high resolution. Nonetheless, we expect that this issue may be easily resolved with engineering of the high-k dielectric trapping layer and/or introduction of alternative layers with better trapping characteristics.

Finally, in Figure 4f we show a combined plot with all 1000 cycles from each case of  $V_{\rm pot}$  (i.e., 1.6, 1.4, 1.2, 1.0 V), to better illustrate the repeatability of the measurements and to clearly indicate the impact  $V_{\rm pot}$  on the synaptic response. As shown, a higher  $V_{\rm pot}$  results in a larger dynamic range, but also increases the abruptness of the pulse-induced conductance modulation (i.e., conductance is changed more with each pulse). In Figure

4f the color-coded solid lines are experimental data and the solid black lines with circles are calculations based on a recursive model for the aligned CNT FET synaptic characteristics. In the following section we provide more details on the model and describe the impact of conductance modulation abruptness and dynamic range on the unsupervised learning pattern recognition function of spiking neural networks.

Unsupervised Learning with Aligned CNT+CMOS Neuromorphic Systems. Synaptic devices such as the charge-trapping aligned CNT FETs are of great interest for the hardware implementation of large-scale neural networks for neuromorphic computing systems. A popular demonstration of the type of functions that can be efficiently implemented on neuromorphic systems is that of pattern recognition based on unsupervised learning in artificial spiking neural networks. Here, we present simulations of pattern recognition using the MNIST handwritten digit data set based on a simplified spiketiming-dependent plasticity scheme modeled on large arrays of aligned CNT synaptic transistors.<sup>64</sup> We utilize an experimentally verified model of the synaptic characteristics of aligned CNT FETs and investigate the impact of the conductance modulation abruptness and dynamic range on recognition rate and on the learning dynamics of the network.

The implementation is illustrated in Figure 5a: The data set consists of  $60\,000$  training images and  $10\,000$  test images. The training images are presented to the network as input voltage pulses which are applied at the rows of the implemented crossbar array architecture. Here, the input vector represents the intensity of all  $28 \times 28$  pixels from the training image, translated into voltage pulses having a width directly proportional to the intensity of the corresponding pixel. At each cross point of the array, the gate of an aligned CNT

synaptic transistor is connected to the input row (presynaptic neuron), and the source is connected to the output column (postsynaptic neuron). The drain is biased to a small negative voltage with respect to the source, to enable current flow in the channel of the aligned CNT FETs. The sum of the currents flowing through all of the synaptic devices connected to each column is summed at the postsynaptic neurons. Mathematically, the current in column j can be expressed using Kirchhoff's current law as  $I_i(t) = \sum_i x_i(t)G_{ii}$ , where  $x_i(t)$  and  $G_{ii}$  are the input voltage pulse and the conductance of the aligned CNT FET from row i. Figure 5b illustrates the output currents from an array with 10 output neurons during the 100 ms that a training image is presented to the network. In the spiking neural network implementation,  $G_{ij}$  is updated based on a simplified spike-timing-dependent plasticity (STDP) scheme.<sup>65</sup> In this STDP scheme, a leaky integrate and fire operation is executed at each output to obtain the neuron potential expressed as  $X_i(t)/dt - X_i(t)/\tau = I_i(t)/\tau$ . When any of the output neuron potentials exceeds a specified threshold  $(X_{th})$ , a postsynaptic spike is triggered, firing the application of voltage pulse at the corresponding column and resetting all  $X_i(t)$  to zero. Figure 5c plots  $X_i(t)$  corresponding to  $I_i(t)$  in Figure 5b, illustrating the triggering of the postsynaptic voltage pulse from the output neuron that first reaches  $X_{th}$  (neuron 2 in this case). Also indicated in Figure 5c is the implementation of lateral inhibition that consists of holding  $X_i(t)$  at zero for neurons other than the one that has last fired for a short period of time (10 ms in this case), to prevent a different neuron from firing in response to the same stimulus (i.e., a winner-takes-all approach).

The firing of the postsynaptic spike delivers a  $V_{gs}$  voltage pulse across the aligned CNT FETs connected to the postsynaptic neuron that has fired, resulting in a chargetrapping-induced update of their channel conductance. This change in the conductance  $(\Delta G)$  is positive or negative depending on the relative timing of the pre- and postsynaptic spikes. In this implementation, synaptic potentiation (i.e., positive  $\Delta G$ ) occurs for all aligned CNT FETs that have an input pulse width  $(t_{in})$  that exceeds the triggering of the postsynaptic spike  $(t_{out})$ , and depression occurs for devices with  $t_{\rm in}$  <  $t_{\rm out}$ . In other words, devices that have an input voltage during the arrival of the output spike will have a small increase in their conductance, and devices without an input voltage during the arrival of the output spike will have a small decrease in their conductance. We note that other implementations aimed at realizing a biologically plausible STDP scheme attempt to achieve a  $\Delta G$  that is proportional to  $\Delta t = t_{\rm in} - t_{\rm out}$ . Instead, we adopt a simplified scheme for practical hardware implementation where  $\Delta G$  is dependent only on the sign of  $\Delta t$  and can be realized with CMOS IC processes, using only square pre- and postsynaptic voltage pulses. Figure 5d shows experimental data and model calculations for  $\Delta G$  resulting from consecutive potentiating and depressing  $V_{gs}$  voltage pulses applied to an aligned CNT synaptic transistor. Calculations are from a recursive model required for spiking neural network simulations where updates in conductance are obtained as

potentiation:

$$\Delta G = \operatorname{pt}(R_{\operatorname{pt}})^{\operatorname{pte}} G$$

(1a)

depression:

$$\Delta G = dp(R_{dp})^{dpe}G$$

(1b)

where

$$R_{\rm pt} = (G_{\rm max} - G)/(G_{\rm max} - G_{\rm min})$$

(2a)

$$R_{dp} = (G - G_{min})/(G_{max} - G_{min})$$

(2b)

In eqs 1 and 2, pt, pte, and  $R_{\rm pt}$  are obtained from fitting the synaptic potentiation characteristics, and dp, dpe, and  $R_{\rm dp}$  are obtained from fitting the synaptic depression characteristics.  $R_{\rm pt}$  and  $R_{\rm dp}$  are associated with the rates at which the conductance is increased/decreased, given the current state of the device as determined by the difference between the conductance and the max/min values. This modeling approach can be used to explore the effects of the synaptic device characteristics on the neuromorphic system-level performance (e.g., in this case recognition rate). The recursive model is similar to those used in previous modeling work, 11,65 but is formulated for easier interpretation and to better bound conductance to the specified  $G_{\rm min}$  and  $G_{\rm max}$ , resulting in improved simulation stability.

In Figure 5e, we present the results of the pattern recognition simulations using the experimentally verified model of the aligned CNT synaptic transistors. The results show the recognition rate as a function of the training number for arrays with 10, 20, 40, and 80 output neurons. Each case is simulated five times, and we plot the mean value including error bars for one standard deviation. For each simulation we present a fraction of the training set images and then perform a recognition test using all 10 000 test images. During the test we keep track of spiking activity and determine the recognition rate a posteriori by assigning each neuron to the digit for which it spiked the most and calculating the ratio of occurrences that the assigned neuron spiked compared to the total number of spikes for a given digit. The results presented in Figure 5e are the average of all digits. Clearly, the recognition rate improves with training and also improves with increasing number of output neurons, as these provide specialization to different styles of handwriting for the same digits, resulting in improved accuracy of the algorithm. Figure 5f plots the recognition rate as a function of the number of output neurons after 60 000 training steps. In Figure 5g, we plot conductance maps for the case of 20 output neurons, which correspond to the conductance of all of the aligned CNT FETs connected to each column in the network (again after all 60 000 training steps).

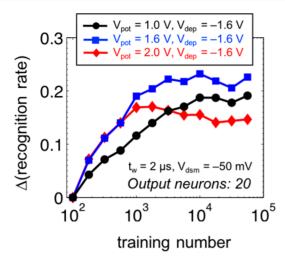

In Figure 4f we present experimental data and model calculations demonstrating the impact of the amplitude of the potentiating voltage pulses  $(V_{pot})$  on the synaptic characteristics of aligned CNT FETs. We showed that increasing  $V_{

m pot}$ resulted in a larger dynamic range, but also increased the abruptness of the conductance modulation. In Figure 6 we now show simulation results from the unsupervised learning pattern recognition using model fits to experimental data from aligned CNT synaptic transistors with increasing  $V_{pot}$ . We calculate the improvement  $(\Delta)$  in recognition rate as a function of training number for the case of  $V_{\text{pot}} = 1.0$  and 1.6 V and also extrapolate the model to the case of  $V_{\rm pot}$  = 2.0 V. The results in Figure 6 show that the increased dynamic range and abruptness in modulation that results from increasing  $V_{\rm pot}$ enhances the initial learning rate of the network (i.e., larger slope during the initial training steps). This enhancement can provide a better recognition rate with a smaller number of training steps (e.g., in the case of  $V_{\rm pot}$  = 1.6 V). However, the detrimental effects of an excessively abrupt conductance modulation resulting from further increasing  $V_{

m pot}$  can quickly

Figure 6. Improvement in recognition rate as a function of training number in aligned CNT FET spiking neural networks with increasing amplitude of potentiating voltage pulses. Learning rate can be optimized to achieve improvements in recognition with reduced number of training cycles.

saturate the improvement in recognition rate (i.e., levels off at a smaller training number), limiting the accuracy achieved in the simulation for  $V_{\rm pot}=2.0$  V. We note that the tuning of pre- and postsynaptic pulses can be applied globally or selectively on the network to enhance/decrease the learning rate of specific neurons and/or input patterns. Thus, the tuning of the synaptic characteristics of aligned CNT FETs presents opportunities for developing neuromorphic systems and unsupervised learning algorithms with adaptive and/or selective learning properties enabled by control of the pre- and postsynaptic pulses.

# **CONCLUSIONS**

We have presented a synaptic transistor technology for the implementation of large-scale neuromorphic systems, based on the wafer-scale CMOS-compatible processing of CNT FETs with highly aligned nanotubes with high semiconducting purity and density. In this paper we analyze the charge-trapping mechanisms responsible for the synaptic properties of aligned CNT FETs and provide a detailed characterization based on DC and pulsed measurements. We measure a large dynamic range (i.e., >10×) with gradual long-term analog programmability of conductance using potentiating and depressing voltage pulses. The robustness of the device operation and stability of the synaptic behavior are demonstrated with multiple cycles of consecutive potentiating/depressing voltage pulses and extraction of programmed conductance states. We also show tuning of the synaptic characteristics of aligned CNT FETs and establish trade-offs in the abruptness and stability of conductance modulation and the dynamic range. On the basis of the demonstrated robustness of the aligned CNT synaptic transistor we simulate the hardware implementation of an unsupervised learning for pattern recognition in spiking neural networks. The simulations are validated with experimental data from measurement-aligned CNT FET synaptic transistors and used to analyze the recognition rate of handwritten digits from the MNIST database. On the basis of the experimentally demonstrated tuning of the aligned CNT FET synaptic response, we show the impact of conductance modulation dynamic range and abruptness on the learning rate. We show

that tuning of the CNT synaptic characteristics enables optimizing the learning rate and achieves higher recognition rate with a lower training number. We also discuss the tuning of aligned CNT synaptic behavior for developing neuromorphic algorithms with adaptive and/or selective learning characteristics.

#### **METHODS**

In this work, a recently improved evaporation-driven process, named floating evaporative self-assembly, 56,57 has been utilized by Carbonics Inc. to fabricate highly aligned SWCNT devices at the wafer level. The deposition method starts with a nanotube "ink" in organic solvent dispensed onto a water surface. As the solution spreads, it intersects the receiving substrate that vertically dissects the water-surface, resulting in CNT alignment occurring at the interface. Extracting the wafer at a controlled rate allows CNTs to coat the deposition area in a dense, aligned monolayer. Semiconducting-nanotube inks prepared by selective conjugated polymer sorting agents are used, leading to exceptional (>99.9%) semiconducting purity. This method deposits nanotubes in an unbundled, isolated morphology, making it possible to form robust electrical contacts to each nanotube and to achieve excellent gate-ability. Using standard processing techniques, the nanotube arrays are fabricated into top-gated aligned CNT FETs with high CNT density (>60 tubes/ $\mu$ m) and self-aligned T-shaped gate structure that enhances gate control, helps scaling down the channel length, and reduces parasitic capacitance (details provided elsewhere). 51,58

#### AUTHOR INFORMATION

## **Corresponding Authors**

\*E-mail: isanchez@isi.edu.

\*E-mail: kos@carbonicsinc.com.

\*E-mail: han.wang.4@usc.edu.

\*E-mail: chongwuz@usc.edu.

## ORCID ®

Ivan Sanchez Esqueda: 0000-0001-6530-8602

Han Wang: 0000-0001-5121-3362 Chongwu Zhou: 0000-0001-8448-8450

#### Note

The authors declare no competing financial interest.

#### **ACKNOWLEDGMENTS**

H.W. would like to acknowledge the support from the Army Research Office Young Investigator Program (Grant no. W911NF-18-1-0268).

# REFERENCES

- (1) Frank, D. J.; Dennard, R. H.; Nowak, E.; Solomon, P. M.; Taur, Y.; Wong, H. P. Device Scaling Limits of Si MOSFETs and Their Application Dependencies. *Proc. IEEE* **2001**, *89*, 259–288.

- (2) King, T. FinFETs for Nanoscale CMOS Digital Integrated Circuits. *IEEE ICCAD* **2005**, 207–210.

- (3) Bohr, M. T.; Young, I. A. CMOS Scaling Trends and Beyond. *IEEE Micro* **2017**, *37*, 20–29.

- (4) Shalf, J. M.; Leland, R. Computing beyond Moore's Law. Computer (Long. Beach. Calif). 2015, 48, 14–23.

- (5) Fiori, G.; Bonaccorso, F.; Iannaccone, G.; Palacios, T.; Neumaier, D.; Seabaugh, A.; Banerjee, S. K.; Colombo, L. Electronics Based on Two-Dimensional Materials. *Nat. Nanotechnol.* **2014**, *9*, 768–779.

- (6) Qiu, C.; Zhang, Z.; Xiao, M.; Yang, Y.; Zhong, D.; Peng, L. Scaling Carbon Nanotube Complementary Transistors to 5-Nm Gate Lengths. *Science (Washington, DC, U. S.)* **2017**, *355*, 271–276.

(7) Desai, S. B.; Madhvapathy, S. R.; Sachid, A. B.; Llinas, J. P.; Wang, Q.; Ahn, G. H.; Pitner, G.; Kim, M. J.; Bokor, J.; Hu, C.; Wong, H.-S. P.; Javey, A. *Science* **2016**, *354*, 99–103.

- (8) Peng, L.; Zhang, Z.; Wang, S. Carbon Nanotube Electronics: Recent Advances. *Mater. Today* **2014**, *17*, 433–442.

- (9) Li, L.; Yu, Y.; Ye, G. J.; Ge, Q.; Ou, X.; Wu, H.; Feng, D.; Chen, X. H.; Zhang, Y. Black Phosphorus Field-Effect Transistors. *Nat. Nanotechnol.* **2014**, *9*, 372–377.

- (10) Yin, C.; Li, Y.; Wang, J.; Wang, X.; Yang, Y.; Ren, T. Carbon Nanotube Transistor with Short-Term Memory. *Tsinghua Sci. Technol.* **2016**, 21, 442–448.

- (11) Kim, S.; Yoon, J.; Kim, H.; Choi, S. Carbon Nanotube Synaptic Transistor Network for Pattern Recognition. *ACS Appl. Mater. Interfaces* **2015**, *7*, 25479–25486.

- (12) Kim, K.; Chen, C.; Truong, Q.; Shen, A. M.; Chen, Y. A Carbon Nanotube Synapse with Dynamic Logic and Learning. *Adv. Mater.* **2013**, 25, 1693–1698.

- (13) Kim, S.; Choi, B.; Lim, M.; Yoon, J.; Lee, J.; Kim, H.-D.; Choi, S.-J. Pattern Recognition Using Carbon Nanotube Synaptic Transistors with an Adjustable Weight Update Protocol. *ACS Nano* **2017**, *11*, 2814–2822.

- (14) Shulaker, M. M.; Saraswat, K.; Wong, H. P.; Mitra, S. Monolithic Three-Dimensional Integration of Carbon Nanotube FETs with Silicon CMOS. In *Symposium on VLSI Technology Diges of Technical Papers*; 2014.

- (15) Shulaker, M. M.; Hills, G.; Park, R. S.; Howe, R. T.; Saraswat, K.; Wong, H. P.; Mitra, S. Three-Dimensional Integration of Nanotechnologies for Computing and Data Storage on a Single Chip. *Nature* **2017**, *547*, 74–78.

- (16) Wei, H.; Patil, N.; Lin, A.; Wong, H. S. P.; Mitra, S. Monolithic Three-Dimensional Integrated Circuits Using Carbon Nanotube FETs and Interconnects. *Technol. Dig. Int. Electron Devices Meet. IEDM* **2009**, 577–580.

- (17) Shulaker, M. M.; Wu, T. F.; Sabry, M. M.; Wei, H.; Wong, H. P.; Mitra, S. Monolithic 3D Integration: A Path From Concept To Reality. Design Automation & Test in Europe Conference and Exhibition 2015, 1197–1202.

- (18) Li, C.; Hu, M.; Li, Y.; Jiang, H.; Ge, N.; Montgomery, E.; Zhang, J.; Song, W.; Dávila, N.; Graves, C. E.; Li, Z.; Strachan, J. P.; Lin, P.; Wang, Z.; Barnell, M.; Wu, Q.; Williams, R. S.; Yang, J. J.; Xia, Q. Analogue Signal and Image Processing with Large Memristor Crossbars. *Nat. Electron.* **2018**, *1*, 52–59.

- (19) Gubbi, J.; Buyya, R.; Marusic, S.; Palaniswami, M. Internet of Things (IoT): A Vision, Architectural Elements, and Future Directions. *Futur. Gener. Comput. Syst.* **2013**, *29*, 1645–1660.

- (20) Merolla, P. A.; Arthur, J. V.; Alvarez-icaza, R.; Cassidy, A. S.; Sawada, J.; Akopyan, F.; Jackson, B. L.; Imam, N.; Guo, C.; Nakamura, Y.; Brezzo, B.; Ivan, V.; Esser, S. K.; Appuswamy, R.; Taba, B.; Amir, A.; Flickner, M. D.; Risk, W. P.; Manohar, R.; et al. A Million Spiking-Neuron Integrated Circuit with a Scalable Communication Network and Interface. *Science (Washington, DC, U. S.)* 2014, 345, 668–673.

- (21) Indiveri, B. G.; Liu, S. Memory and Information Processing in Neuromorphic Systems. *Proc. IEEE* **2015**, *103*, 1379–1397.

- (22) Kim, K.; Gaba, S.; Wheeler, D.; Cruz-albrecht, J. M.; Hussain, T.; Srinivasa, N.; Lu, W. A Functional Hybrid Memristor Crossbar-Array/CMOS System for Data Storage and Neuromorphic Applications. *Nano Lett.* **2012**, *12*, 389–395.

- (23) Luo, Q.; Xu, X.; Liu, H.; Lv, H.; Gong, T.; Long, S.; Liu, Q.; Sun, H.; Banerjee, W.; Li, L.; Gao, J.; Lu, N.; Liu, M. Super Non-Linear RRAM with Ultra-Low Power for 3D Vertical Nano-Crossbar Arrays. *Nanoscale* **2016**, *8*, 15629–15636.

- (24) Xia, L.; Gu, P.; Li, B.; Tang, T.; Yin, X.; Huangfu, W.; Yu, S.; Cao, Y.; Wang, Y.; Yang, H. Technological Exploration of RRAM Crossbar Array for Matrix-Vector Multiplication. *J. Comput. Sci. Technol.* **2016**, *31*, 3–19.

- (25) Prezioso, M.; Hoskins, B. D.; Adam, G. C.; Likharev, K. K.; Strukov, D. B. Training and Operation of an Integrated Neuro-

morphic Network Based on Metal-Oxide Memristors. *Nature* **2015**, 521, 61-64.

- (26) Yang, J. J.; Strukov, D. B.; Stewart, D. R. Memristive Devices for Computing. *Nat. Nanotechnol.* **2013**, *8*, 13–24.

- (27) Sheridan, P. M.; Cai, F.; Du, C.; Ma, W.; Zhang, Z.; Lu, W. D. Sparse Coding with Memristor Networks. *Nat. Nanotechnol.* **2017**, *12*, 784–790.

- (28) Cheng, K.; Strukov, D. B. 3D CMOS-Memristor Hybrid Circuits: Devices, Integration, Architecture, and Applications. *International Symposium on Physical Design (ISPD)* **2012**, 33–40.

- (29) Park, S.; Noh, J.; Choo, M.; Sheri, A. M.; Chang, M.; Kim, Y.-B.; Kim, C. J.; Jeon, M.; Lee, B.-G.; Lee, B. H.; Hwang, H. Nanoscale RRAM-Based Synaptic Electronics: Toward a Neuromorphic Computing Device. *Nanotechnology* **2013**, *24*, 384009.

- (30) Jo, S. H.; Chang, T.; Ebong, I.; Bhadviya, B. B.; Mazumder, P.; Lu, W. Nanoscale Memristor Device as Synapse in Neuromorphic Systems. *Nano Lett.* **2010**, *10*, 1297–1301.

- (31) Chang, T.; Kim, S. J. K.; Sheridan, P.; Gaba, S.; Lu, W. Synaptic Behaviors and Modeling of a Metal Oxide Memristive Device. *Appl. Phys. A: Mater. Sci. Process.* **2011**, *102*, 857–863.

- (32) Wang, C.; He, W.; Tong, Y.; Zhao, R. Investigation and Manipulation of Different Analog Behaviors of Memristor as Electronic Synapse for Neuromorphic Applications. *Sci. Rep.* **2016**, *6*, 1–9.

- (33) Wong, H. S. P.; Lee, H. Y.; Yu, S.; Chen, Y. S.; Wu, Y.; Chen, P. S.; Lee, B.; Chen, F. T.; Tsai, M. J. Metal-Oxide RRAM. *Proc. IEEE* **2012**, *100*, 1951–1970.

- (34) Fantini, A.; Goux, L.; Degraeve, R.; Wouters, D. J.; Raghavan, N.; Kar, G.; Belmonte, A.; Chen, Y.; Govoreanu, B.; Jurczak, M. Intrinsic Switching Variability in HfO 2 RRAM. *IEEE International Memory Workshop* **2013**, 1–4.

- (35) Yu, S.; Gao, B.; Fang, Z.; Yu, H.; Kang, J.; Wong, H. P. Stochastic Learning in Oxide Binary Synaptic Device for Neuromorphic Computing. *Front. Neurosci.* **2013**, *7*, 1–9.

- (36) Brivio, S.; Covi, E.; Serb, A.; Prodromakis, T.; Fanciulli, M.; Spiga, S.; Brivio, S.; Covi, E.; Serb, A.; Prodromakis, T.; Fanciulli, M.; Spiga, S. Experimental Study of Gradual/Abrupt Dynamics of HfO2-Based Memristive Devices. *Appl. Phys. Lett.* **2016**, *109*, 133504.

- (37) Wu, X.; Saxena, V. Enabling Bio-Plausible Multi-Level STDP Using CMOS Neurons with Dendrites and Bistable RRAMs. *Int. Jt. Conf. Neural Networks* **2017**, 3522–3526.

- (38) Covi, E.; Brivio, S.; Serb, A.; Prodromakis, T.; Fanciulli, M.; Spiga, S. Analog Memristive Synapse in Spiking Networks Implementing Unsupervised Learning. *Front. Neurosci.* **2016**, *10*, 1–13.

- (39) Li, Y.; Zhang, M.; Long, S.; Teng, J.; Liu, Q.; Lv, H.; Miranda, E.; Sune, J.; Liu, M. Investigation on the Conductive Filament Growth Dynamics in Resistive Switching Memory *via* a Universal Monte Carlo Simulator. *Sci. Rep.* **2017**, *7*, 1–11.

- (40) Sidler, S.; Boybat, I.; Shelby, R. M.; Narayanan, P.; Jang, J.; Fumarola, A.; Moon, K.; Leblebici, Y.; Hwang, H.; Burr, G. W. Large-Scale Neural Networks Implemented with Non-Volatile Memory as the Synaptic Weight Element: Impact of Conductance Response. *European Solid-State Device Research Conference (ESSDERS)* 2016, 440–443.

- (41) Kim, S.; Choi, S.; Lu, W. Comprehensive Physical Model of Dynamic Resistive Switching in an Oxide Memristor. *ACS Nano* **2014**, *8*, 2369–2376.

- (42) Acharyya, D.; Hazra, A.; Bhattacharyya, P. Microelectronics Reliability A Journey towards Reliability Improvement of TiO 2 Based Resistive Random Access Memory: A Review. *Microelectron. Reliab.* **2014**, *54*, 541–560.

- (43) Mustaqima, M.; Yoo, P.; Huang, W.; Lee, B. W.; Liu, C. Regulation of the Forming Process and the Set Voltage Distribution of Unipolar Resistance Switching in Spin-Coated CoFe2O4 Thin Films. *Nanoscale Res. Lett.* **2015**, *10*, 1–7.

- (44) Gu, X.; Iyer, S. S. Unsupervised Learning Using Charge-Trap Transistors. *IEEE Electron Device Lett.* **2017**, *38*, 1204–1207.

I

(45) Shulaker, M. M.; Hills, G.; Patil, N.; Wei, H.; Chen, H.; Wong, H. P.; Mitra, S. Carbon Nanotube Computer. *Nature* **2013**, *501*, 526–530.

- (46) Shulaker, M. M.; Wei, H.; Mitra, S.; Wong, H.-S. P. Carbon Nanotubes for Monolithic 3D ICs. *Carbon Nanotubes for Interconnects* **2017**, 315–333.

- (47) Liu, F.; Member, S.; Wang, K. L.; Li, C.; Zhou, C. Study of Random Telegraph Signals in Single-Walled Carbon Nanotube Field Effect Transistors. *IEEE Trans. Nanotechnol.* **2006**, *5*, 441–445.

- (48) Bushmaker, A. W.; Oklejas, V.; Walker, D.; Hopkins, A. R.; Chen, J.; Cronin, S. B. Single-Ion Adsorption and Switching in Carbon Nanotubes. *Nat. Commun.* **2016**, *7*, 1–8.

- (49) Esqueda, I. S.; Cress, C. D.; Cao, Y.; Che, Y.; Fritze, M.; Zhou, C. The Impact of Defect Scattering on the Quasi-Ballistic Transport of Nanoscale Conductors. *J. Appl. Phys.* **2015**, *117*, 084319.

- (50) Han, S.; Tang, J.; Kumar, B.; Falk, A.; Farmer, D.; Tulevski, G.; Jenkins, K.; Afzali, A.; Oida, S.; Ott, J.; Hannon, J.; Haensch, W. High-Speed Logic Integrated Circuits with Solution-Processed Self-Assembled Carbon Nanotubes. *Nat. Nanotechnol.* **2017**, *12*, 861–865.

- (51) Che, Y.; Lin, Y. C.; Kim, P.; Zhou, C. T-Gate Aligned Nanotube Radio Frequency Transistors and Circuits with Superior Performance. *ACS Nano* **2013**, *7*, 4343–4350.

- (52) Rueckes, T.; Kim, K.; Joselevich, E.; Tseng, G. Y.; Cheung, C.; Lieber, C. M. Carbon Nanotube Based Nonvolatile Random Access Memory for Molecular Computing. *Science (Washington, DC, U. S.)* **2000**, *289*, 94–98.

- (53) Kang, S. J.; Kocabas, C.; Ozel, T.; Shim, M.; Pimparkar, N.; Alam, M. A.; Rotkin, S. V.; Rogers, J. A. High-Performance Electronics Using Dense, Perfectly Aligned Arrays of Single-Walled Carbon Nanotubes. *Nat. Nanotechnol.* **2007**, *2*, 230–236.

- (54) Patil, N.; Lin, A.; Zhang, J.; Wei, H.; Anderson, K.; Wong, H. P.; Mitra, S. VMR: VLSI-Compatible Metallic Carbon Nanotube Removal for Imperfection-Immune Cascaded Multi-Stage Digital Logic Circuits Using Carbon Nanotube FETs. *IEEE International Electron Devices Meeting* **2009**, 573–576.

- (55) Che, Y.; Chen, H.; Gui, H.; Liu, J.; Liu, B.; Zhou, C. Review of Carbon Nanotube Nanoelectronics and Macroelectronics. *Semicond. Sci. Technol.* **2014**, *29*, 1–17.

- (56) Jinkins, K. R.; Chan, J.; Brady, G. J.; Gronski, K. K.; Gopalan, P.; Evensen, H. T.; Arnold, M. S. Nanotube Alignment Mechanism in Floating Evaporative Self-Assembly. *Langmuir* **2017**, *33*, 13407–13414.

- (57) Joo, Y.; Brady, G. J.; Arnold, M. S.; Gopalan, P. Dose-Controlled, Floating Evaporative Self-Assembly and Alignment of Semiconducting Carbon Nanotubes from Organic Solvents. *Langmuir* **2014**, *30*, 3460–3466.

- (58) Che, Y.; Badmaev, A.; Jooyaie, A.; Wu, T.; Zhang, J.; Wang, C.; Galatsis, K.; Enaya, H. A.; Zhou, C. Self-Aligned T-Gate High-Purity Semiconducting Carbon Nanotube RF Transistors Operated in Quasi-Ballistic Transport and Quantum Capacitance Regime. ACS Nano 2012, 6, 6936–6943.

- (59) Esqueda, I. S.; Cress, C. D.; Che, Y.; Cao, Y.; Zhou, C. Charge Trapping in Aligned Single-Walled Carbon Nanotube Arrays Induced by Ionizing Radiation Exposure. *J. Appl. Phys.* **2014**, *115*, 54506.

- (60) Rutherglen, C.; Jain, D.; Burke, P. Nanotube Electronics for Radiofrequency Applications. *Nat. Nanotechnol.* **2009**, *4*, 811–819.

- (61) Park, R. S.; Shulaker, M. M.; Hills, G.; Liyanage, L. S.; Lee, S.; Tang, A.; Mitra, S.; Wong, H. P. Hysteresis in Carbon Nanotube Transistors: MEasurement and Analysis of Trap Density, Energy Level, and Spatial Distribution. *ACS Nano* **2016**, *10*, 4599–4608.

- (62) Wu, Y.; Yu, S.; Wong, H. S. P. AlOx-Based Resistive Switching Device with Gradual Resistance Modulation for Neuromorphic Device Application. In *IEEE International Memory Workshop*; 2012.

- (63) Sarkar, B.; Lee, B.; Misra, V. Understanding the Gradual Reset in Pt/Al2O3/Ni RRAM for Synaptic Applications. *Semicond. Sci. Technol.* **2015**, *30*, 105014.

- (64) Lecun, Y.; Bottou, L.; Bengio, Y.; Haffner, P. Gradient-Based Learning Applied to Document Recognition. *Proc. IEEE* **1998**, *86*, 1–46.

(65) Querlioz, D.; Bichler, O.; Dollfus, P.; Gamrat, C. Immunity to Device Variations in a Spiking Neural Network With Memristive Nanodevices. *IEEE Trans. Nanotechnol.* **2013**, *12*, 288–295.