Facile Five-Step Heteroepitaxial Growth of

GaAs Nanowires on Si Substrates and the

Twin Formation Mechanism

Maoqing Yao<sup>†,||</sup>, Chunyang Sheng<sup>‡,||</sup>, Mingyuan Ge<sup>§</sup>, Chun-Yung Chi<sup>†,||</sup>, Sen Cong<sup>†,||</sup>,

Aiichiro Nakano<sup>‡, ||</sup>, P. Daniel Dapkus<sup>†, ||\*</sup> and Chongwu Zhou<sup>†, ||\*</sup>

†Ming Hsieh Department of Electrical Engineering, ‡Collaboratory for Advanced

Computing and Simulations, Department of Physics and Astronomy, Department of

Computer Science, and Department of Chemical Engineering and Materials Science,

§Mork Family Department of Chemical Engineering and Materials Science, || Center

for Energy Nanoscience, University of Southern California, Los Angeles, California

90089, United States

**Corresponding Author**

\*E-mail: (C.Z.) chongwuz@usc.edu

\*E-mail: (P.D.D.) dapkus@usc.edu

**Supporting Information**

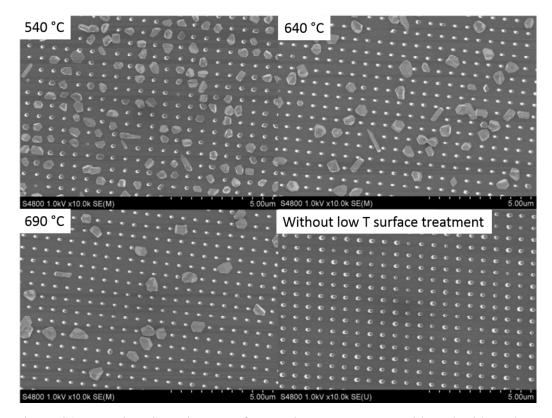

Figure S1. Top view SEM images of nanowire arrays grown with and without low surface treatment step prior to the nanowire growth. Surface treatment step is 4 minutes if there is.

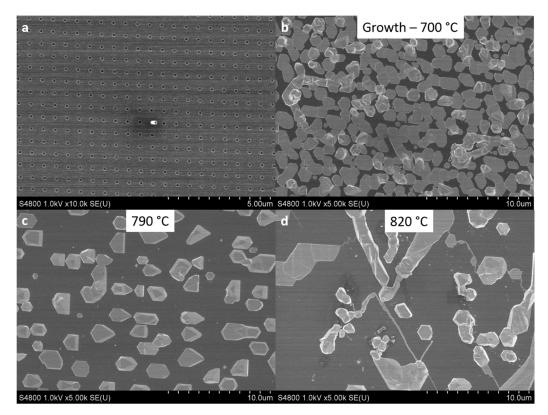

Figure S2. (a) Top view SEM image of sample after growth at 820 °C. Few nanowires can be obtained. (b) – (d) Top view SEM images of bare Si region after nanowire growth at (b) 700 °C, (c) 790 °C and (d) 820 °C. Island density decreased due to increased Ga diffusion length. In (d) we can see the trace left by large mobile Ga balls.

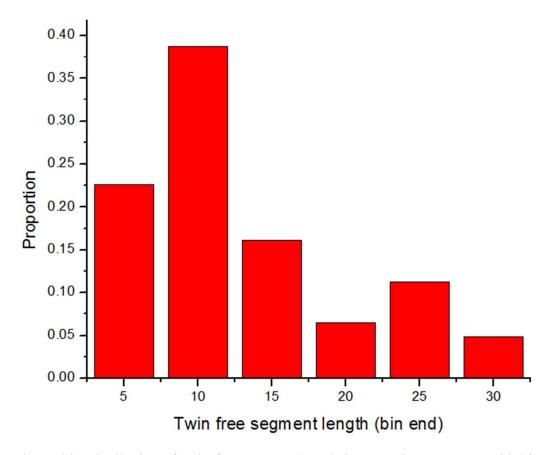

Figure S3. Distribution of twin free segment length in nanowires grown at 790 °C shown in Figure 4b of main text.

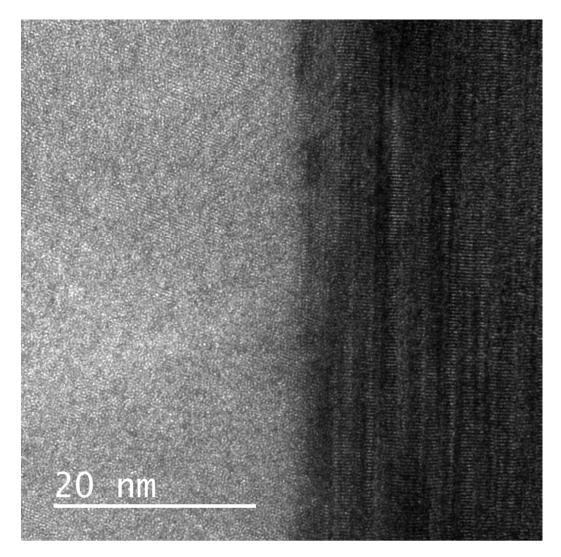

Figure S4. High resolution TEM image at the interface of Si and GaAs of the sample shown in Figure 4c in the main text. The initial part of GaAs nanowire is grown at 760 °C. At some location the twin density is as high as every monolayer, so the crystal structure is effectively Wurtzite.

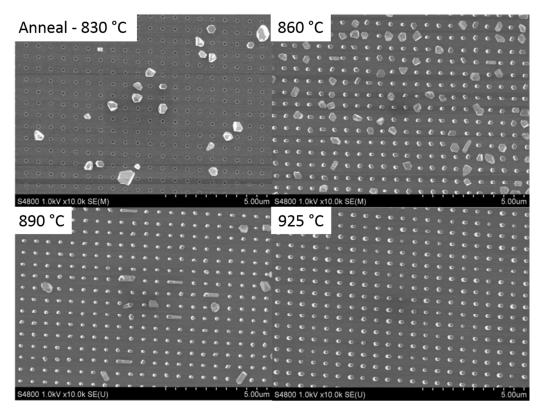

Figure S5. Top view SEM images of GaAs nanowire arrays grown on Si with different hydrogen annealing temperatures. Other conditions are all the same as described in text. Lower annealing temperatures reduce vertical nanowire yield