### Imperceptible and Ultra-Flexible P-Type Transistors and Macroelectronics Based on Carbon Nanotubes

Xuan Cao<sup>1, \*</sup>, Yu Cao<sup>2, \*</sup> and Chongwu Zhou<sup>1, 2, #</sup>

<sup>1</sup> Department of Chemical Engineering and Materials Science, University of Southern California, Los Angeles, CA, 90089, USA.

<sup>2</sup> Department of Electrical Engineering, University of Southern California, Los Angeles, CA, 90089, USA.

\* These authors contributed equally to the work.

# To whom correspondence should be addressed. E-mail <u>chongwuz@usc.edu</u>

#### **S0.** Tensile strain calculation

To calculate the tensile strain when the single wall carbon nanotube (SWNT) electronic foil was wrapped tightly around a cylinder with radius ~ 220  $\mu$ m, we used the following formula<sup>1</sup>:

$$\varepsilon = \frac{1}{R} \times \frac{d_s + d_f}{2} \times \frac{\chi \cdot \gamma^2 + 2 \cdot \chi \cdot \gamma + 1}{\chi \cdot \gamma^2 + \chi \cdot \gamma + \gamma + 1}$$

In the above formula, *R* is the bending radius,  $d_s$  is the thickness of the substrate, and  $d_f$  is the thickness of SWNT thin-film transistor (TFT).  $\gamma = d_f/d_s$  and  $\chi = Y_f/Y_s$  where  $Y_f$  and  $Y_s$  are the Young's modulus of SWNT TFT and the substrate, respectively. We assume  $Y_f = Y_s$  and the above formula can be further simplified:

$$\varepsilon = \frac{1}{R} \times \frac{d_s + d_f}{2}$$

The thickness of the substrate is  $1.4\mu m$  and the total thickness of SWNT TFT is less than 200 nm. With the bending radius ~ 220  $\mu m$ , the tensile strain is calculated to be ~ 0.3%. If the bending radius is decreased to ~ 40  $\mu m$ , the tensile strain will be increased to ~ 2.7%.

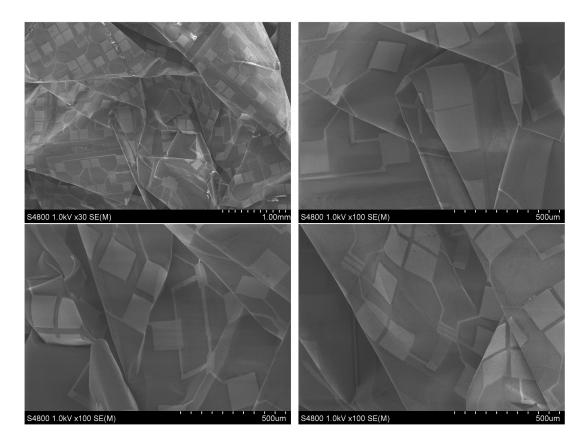

### S1. Scanning electron microscope images of a crumpled electronic foil

Figure S1 shows four scanning electron microscope (SEM) images of a crumpled electronic foil.

Figure S1| SEM images of a crumpled electronic foil.

## **S2.** Gate leakage current and electrical parameters of the representative device under three conditions

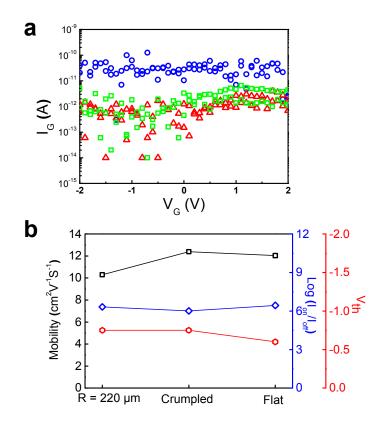

Figure S2a shows the gate leakage current for the representative SWNT TFT in Figure 3c under three conditions: relaxed status (flat), bent with radius of curvature ~ 220  $\mu$ m, and after crumpling. The gate leakage currents of the TFT at bent and relaxed status exhibited no identifiable difference, while the gate leakage current of the crumpled TFT showed an increase by a factor of 10.

Figure S2b shows electrical parameters (mobility, logarithm on-off ratio and threshold voltage) for the representative SWNT TFT in Figure 3c under three conditions: relaxed status (flat), bent with radius of curvature ~ 220  $\mu$ m, and after crumpling. The mobility remained between 10 and 12 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>, the on/off ratio remained more than 10<sup>6</sup>, and the shift of the threshold voltage was less than 0.2 V.

Figure S2 | Gate leakage current and electrical parameters of the representative device under three conditions. (a) Gate leakage currents of the representative TFT with L = 10  $\mu$ m and W = 100  $\mu$ m under relaxed (flat) state, after crumpling, and bent with radius ~ 220  $\mu$ m. (b) Mobility, on-off ratio, and threshold voltage of the same SWNT TFT under relaxed (flat) state, after crumpling, and bent with radius ~ 220  $\mu$ m.

# S3. Gate leakage current for the representative SWNT TFT under different compressive strains

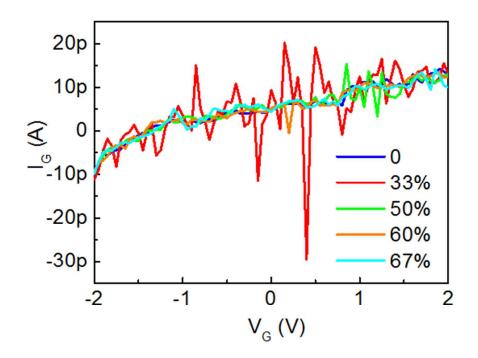

Figure S3 shows the gate leakage current for the representative SWNT TFT in Figure 4c under different compressive strains (0, 33%, 50%, 60% and 67%). There is no significant change in the gate leakage current, indicating no gate dielectric degradation of SWNT TFTs under various compressive strains.

Figure S3| Gate leakage current of a SWNT TFT with  $L = 50 \mu m$  and  $W = 100 \mu m$  undergoing 0, 33%, 50%, 60% and 67% compressive strains.

# S4. Scanning electron microscope images of SWNT circuits with 33% compressive strain

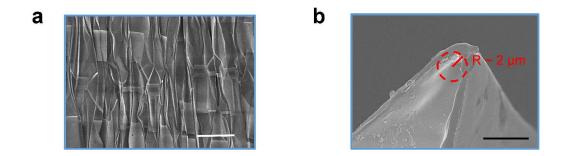

Figure S4 shows the SEM images of SWNT circuits when we applied 33% compressive strain to the fabricated SWNT electronic foil. Top-view SEM image in Figure S4a shows out-of-plane wrinkles formed for the SWNT circuits when we applied 33% compressive strain to the SWNT electronic foil. Cross-section SEM image in Figure S4b shows the smallest bending radius with a local bending radius  $\sim 2 \mu m$ . We note that while devices with local bending radius down to 40  $\mu m$  showed ultra-flexibility and mechanical robustness, finer wrinkles with even smaller bending radius would lead to failure of devices.

Figure S4| SEM images of SWNT electronic foil on elastomer undergoing 33% compressive strain, showing wrinkled mirco-structure. (a) top-view of the wrinkled plasitic electronics. Scale bar is 200  $\mu$ m. (b) Cross-section view of a tiny wrinkle, indicating radius of curvature ~ 2  $\mu$ m. Scale bar is 5  $\mu$ m.

### Reference

1. Salvatore, G. A.; Munzenrieder, N.; Kinkeldei, T.; Petti, L.; Zysset, C.; Strebel, I.; Buthe, L.; Troster, G. Wafer-Scale Design of Lightweight and Transparent Electronics That Wraps around Hairs. *Nat. Commun.* **2014**, *5*, 2982-2589.