# An RTD/Transistor Switching Block and Its Possible Application in Binary and Ternary Adders

J. L. Huber, J. Chen, J. A. McCormack, C. W. Zhou, and M. A. Reed, Senior Member, IEEE

Abstract— We propose and demonstrate both a binary and ternary adder circuit based on a resonant tunneling diode (RTD) and a bipolar transistor. The basic switching cell consists of an RTD in series with the base of a bipolar transistor. The RTD is used to set a threshold voltage for the switching of the transistor.

#### I. INTRODUCTION

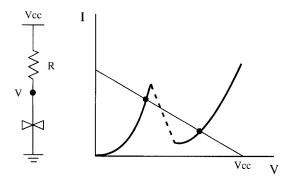

THE peaked current–voltage (I-V) characteristic of Esaki tunnel diodes allows implementation of both binary and multistate logic with fewer devices than conventional transistor circuits. The simplest demonstration of this is when a resistor acts as a load for a tunnel diode (Fig. 1). If the resistor has a larger value than the average negative differential resistance (NDR) the load line intersects the RTD I-V characteristics more than once, allowing two stable operating points for the circuit exist.

The application of the NDR characteristics of Esaki tunnel diodes to digital switching circuits was recognized and demonstrated shortly following the first demonstration of the tunnel diode [1]. However, the large junction capacitance and difficulty in fabrication of uniform Esaki tunnel diodes proved to be a stumbling block for integrated circuits [2], [3].

Precisely controlled semiconductor heterostructure epitaxial growth techniques have lead to the development of the resonant tunneling diode (RTD) which has a similar peaked I-V characteristic [4], [5]. Multiple RTD's can be integrated in series to produce a multiple peaked structure [6]. RTD's do not suffer from the same problems as Esaki tunnel diodes and have been used to implement a number of different circuit designs [7]–[10].

In addition to discrete RTD's, integration of RTD's with conventional transistor structures into a single three-terminal device has been demonstrated [11]–[13]. The advantage of this approach is the decoupling of the output from the input that is associated with three-terminal operation while retaining the peaked I-V characteristics. The disadvantage is that of increased fabrication complexity for certain configurations.

We propose and demonstrate a simple yet flexible switching configuration using a single discrete RTD and a single transistor. In this configuration, the RTD is responsible for the multiple switching but does not set the operating logic levels.

Manuscript received August 28, 1996; revised July 31, 1997. The review of this paper was arranged by Editor K. M. Lau.

- J. L. Huber is with Digital Semiconductor, Hudson, MA 01749 USA.

- J. Chen, C. W. Zhou, and M. A. Reed are with the Center for Microelectronic Materials and Structures, Yale University, New Haven, CT 06520 USA.

- J. A. McCormack is with Hewlett-Packard, Fort Collins, CO 80528-9599 USA.

Publisher Item Identifier S 0018-9383(97)08288-9.

Fig. 1.  $I\!-\!V$  characteristics of an RTD using a single load resistor. The NDR region of the RTD allows two stable operating points to exist for the same circuit. The point lying on the NDR region is not stable.

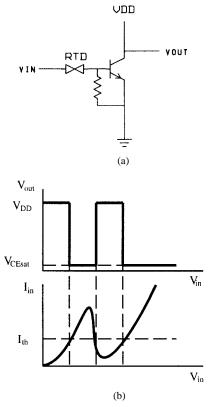

Fig. 2. (a) Schematic of the switching block. (b) Transfer function of the switching block compared with the RTD transfer function.

This approach eliminates uncertainty in logic levels due to fluctuations in individual RTD characteristics, increasing the noise margin for each state.

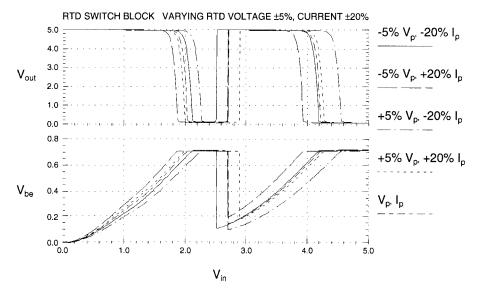

Fig. 3. Simulation of the output voltage ( $V_{\rm DD}=5$  V) and the transistor base-emitter voltage for different RTD I-V characteristics. The peak current/voltage of the RTD was varied by  $\pm 20\% (\pm 5\%)$ .

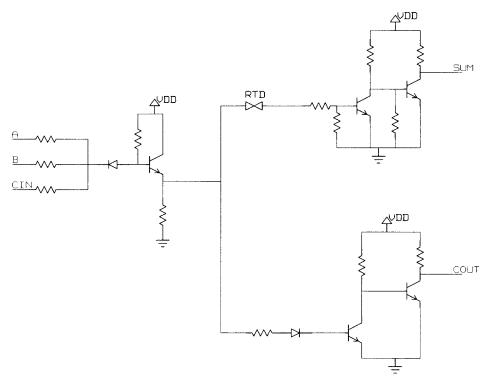

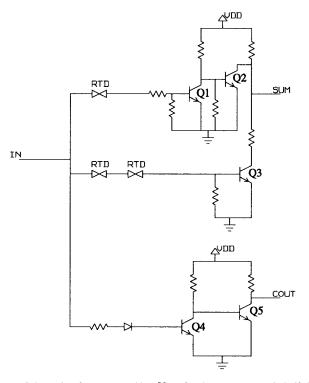

Fig. 4. Schematic of a full binary adder using the RTD/transistor switching block.

# II. RTD/TRANSISTOR SWITCHING BLOCK

The basic switching block is shown in Fig. 2(a). A schematic of the transfer function is shown in Fig. 2(b). The multiple switching results from the nonlinear RTD I-V characteristics, while the transistor acts as both an output buffer to the RTD, and a source of gain. An input buffer (not shown) is required for a constant input impedance.

When  $V_{\rm in}$  is zero, the transistor is off, and  $V_{\rm out}$  will be  $V_{\rm DD}$ . As  $V_{\rm in}$  is increased, the voltage across the transistor base-emitter junction will linearly increase as determined by the shunt resistance, assuming the base impedance of the transistor is much greater than the shunt resistance. Once the

input current is large enough that the voltage drop across the shunt resistor is equal to the turn-on voltage for the base-emitter junction, the transistor will begin to draw the excess input current, the transistor will be forced into saturation, and  $V_{\rm out}$  will be forced to  $V_{C\rm Esat}$ .

At some point, the voltage drop across the RTD will increase such that it is operating in the NDR region (i.e., the dynamic resistance will increase), and the input current will drop sharply, turning off the transistor, thus switching  $V_{\rm out}$  back to  $V_{\rm DD}$ . When the input current again exceeds the threshold value, the transistor will turn on, and  $V_{\rm out}$  will switch back to  $V_{\rm CEsat}$ .

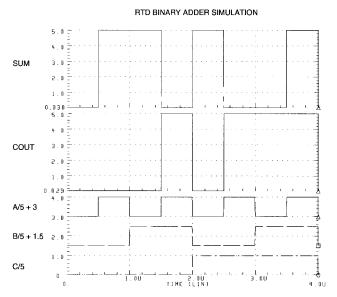

Fig. 5. Simulation of the full adder. The inputs A,B,C scaled to fit on the same set of axes.

Fig. 6. Schematic of a ternary adder.  $V_{\rm DD}$  for the carry output is half that for the sum output.

Small fluctuations on the order of a single monolayer in the epitaxial structure used to form an RTD can cause relatively large fluctuations in both its peak current and peak voltage characteristics [14], [15]. The uncertainty of these parameters reduces the robustness of RTD circuits using resistive and RTD loads. The threshold nature of the switching element described here helps to reduce the effects of those fluctuations. The voltage at which the threshold is reached can be set by choosing the appropriate value for the shunt resistor.

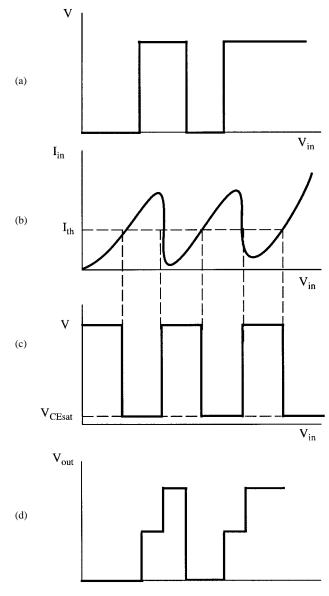

Fig. 7. Various transfer function schematics for transistors in the ternary adder circuit. (a) Schematic of transfer function of Q2. (b) Input current to switching block with two RTD's in series (i.e., Q3). (c) Collector voltage for Q3. (d) Sum voltage for the circuit.

Fig. 3 shows the output of the switching block for different RTD I-V characteristics. The peak current (voltage) can vary by as much as  $\pm 20\%(\pm 5\%)$  and still produce the same output voltage for input voltages of, for example, 1.25, 2.5, 3.75, and 5 V which are easily producible by using a resistive ladder network to generate  $V_{\rm in}$ . Because the output voltages are generated by sources external to the RTD, there is no uncertainty in operating voltage levels resulting from fluctuations in the RTD I-V characteristics, and hence, errors are not propagated through a circuit consisting of a number of switching blocks in series.

A disadvantage to the switching block as described is that it relies on forcing the output of a transistor into hard saturation. This can be eliminated while still obtaining identical functionality, at the cost of more transistors, by replacing the transistor with an emitter coupled pair.

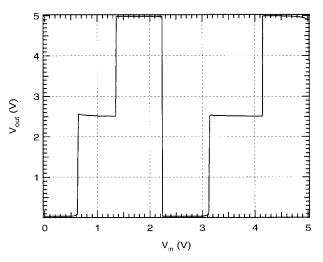

Fig. 8. Measured transfer function for the ternary adder circuit.

### III. ADDER CIRCUITS

### A. Binary Adder

The usefulness of this switching block is demonstrated in Fig. 4, which is a full adder, including carry bit. The simulated output is shown in Fig. 5. A full adder, built using conventional architectures requires  $25 \sim 30$  transistors. The circuit shown here uses five, plus one RTD. Of those five, three function as buffers and/or invertors. The sum bit is simply the switching element with an inverter to give the correct polarity. The carry bit is a saturable amplifier. Advantages of the reduced device count are more functionality for the same on chip area, or reduced fabrication tolerances for a given amount of functionality area density.

With proper choice of output stages, the lower output voltage could be set very near to 0 V, implying a large on/off voltage ratio. It is important to note that this does not achieve the same low power dissipation as is generally associated with efforts to increase the peak/valley current ratio of RTD's. This is because in the circuit, even when the output voltage is low, there is still current flowing through the RTD (and the shunt resistor). Thus the valley current of the RTD is still the limiting factor to low power dissipation.

## B. Ternary Adder

Increasing the number of logic levels used in a circuit can further reduce the number devices required for a given functionality and/or complexity of the device interconnect scheme [16]. An RTD based ternary adder has previously been demonstrated [17]. That circuit was a clock based circuit where the output voltages were determined directly by a resistive load line on an RTD.

We demonstrate a ternary adder using two switching blocks, one with a slight modification with respect to the other. The circuit, shown in Fig. 6, has the same advantages as those described for the binary adder. The first block consists of Q1, and an inverter, Q2. The transfer function for this stage only is shown in Fig. 7(a). When two appropriately sized RTD's are connected in series, a multiple peaked I-V characteristic is

obtained, as shown in Fig. 7(b). This adds an extra switching cycle to the transistor Q3. The thresholds are set such that Q3 initially switches before Q1 (and hence Q2). The full circuit transfer function is obtained as follows: When Q1 is off, Q2 is on and the sum is low, regardless of Q3. When Q1 is on, and Q2 is off, the output is high if Q3 is off. However, if Q2 is off and Q3 is on, the output is midway between high and low, assuming the collector resistors for Q2 and Q3 are equal. The *measured* transfer function for the circuit is shown in Fig. 8.

### IV. CONCLUSION

We have demonstrated the switching characteristics of a simple switching block based on a single RTD and a single transistor. The configuration switches when a threshold current through the RTD is obtained, decreasing the variability from RTD peak current and voltage fluctuations. The switching block was used to build both a binary and a ternary adder with a minimum number of active circuit elements.

#### REFERENCES

- J. M. Carroll, Tunnel-Diodes and Semiconductor Circuits. New York: McGraw-Hill, 1963.

- [2] M. N. S. Swamy, "A high-speed tunnel-diode scaler," *Electron. Eng.*, vol. 37, pp. 225–229, 1965.

- [3] Z. C. Tan and J. B. Earnshaw, "Series-connected tunnel-diode-scaler design considerations," *Electron. Eng.*, vol. 39, pp. 624–629, 1967.

- [4] L. L. Chang, L. Esaki, and R. Tsu, "Resonant tunneling in semiconductor double barriers," *Appl. Phys. Lett.*, vol. 24, no. 12, pp. 593–595, 1974.

- [5] T. J. Shewchuk, P. C. Chapin, P. D. Coleman, W. Kopp, R. Fischer, and H. Morkoç, "Resonant tunneling oscillations in a GaAs-Al<sub>x</sub> Ga<sub>1-x</sub>As heterostructure at room temperature," *Appl. Phys. Lett.*, vol. 46, no. 5, pp. 508–510, 1985.

- [6] R. C. Potter, A. A. Lakhani, D. Beyea, E. Hempling, and A. Fathimulla, "Three-dimensional integration of resonant tunneling structures for signal processing and three-state logic," *Appl. Phys. Lett.*, vol. 52, pp. 2163–2165, 1988.

- [7] T. H. Kuo, H. C. Lin, R. C. Potter, and D. Schupe, "Multiple-valued counter," *IEEE Trans. Comput.*, vol. 42, pp. 106–109, 1993.

- [8] A. C. Seabaugh, Y. C. Kao, and H. T. Yuan, "Nine-state resonant tunneling diode memory," *IEEE Electron Device Lett.*, vol. 13, pp. 479–481, Sept. 1992.

- [9] S. Sen, F. Capasso, A. Y. Cho, and D. Sivco, "Resonant tunneling device with multiple negative differential resistance: Digital and signal processing applications with reduced circuit complexity," *IEEE Trans. Electron Devices*, vol. ED-34, pp. 2185–2191, Oct. 1987.

- Electron Devices, vol. ED-34, pp. 2185–2191, Oct. 1987.

[10] J. R. Söderström and T. G. Anderson, "A multiple-state memory cell based on the resonant tunneling diode," *IEEE Electron Device Lett.*, vol. 9, pp. 200–202, May 1988.

- [11] F. Capasso, S. Sen, F. Beltram, L. M. Lunardi, A. S. Vengurlekar, P. R. Smith, N. J. Shah, R. J. Malik, and A. Y. Cho, "Quantum functional devices: Resonant-tunneling transistors, circuits with reduced complexity, and multiple-valued logic," *IEEE Trans. Electron Devices*, vol. 36, pp. 2065–2081, Oct. 1989.

- [12] T. S. Moise, A. C. Seabaugh, E. A. Beam, and J. N. Randall, "Room-temperature operation of a resonant-tunneling hot-electron transistor based integrated circuit," *IEEE Electron Device Lett.*, vol. 14, pp. 441–443, Sept. 1993.

- [13] A. C. Seabaugh, III, E. A. Beam, A. H. Taddiken, J. N. Randall, and Y. C. Kao, "Co-integration of resonant tunneling and double heterojucntion bipolar transistors on InP," *IEEE Electron Device Lett.*, vol. 14, pp. 472–474, Oct. 1993.

- [14] M. A. Reed, W. R. Frensley, W. M. Duncan, R. J. Matyi, A. C. Seabaugh, and H.-L. Tsai, "Quantitative resonant tunneling spectroscopy: Current–voltage characteristics of precisely characterized resonant tunneling diodes," *Appl. Phys. Lett.*, vol. 54, no. 13, pp. 1256–1258, 1989.

- [15] M. A. Reed, J. W. Lee, R. K. Aldert, and A. E. Wetsel, "Investigation of quantum well and tunnel barrier growth by resonant tunneling," J. Mater. Res., vol. 1, no. 2, pp. 337–346, 1986.

- [16] K. C. Smith, "The prospects for multivalued logic: A technology and application view," *IEEE Trans. Comput.*, vol. C-30, pp. 619–634, 1981.

- [17] S. J. Wei and H. C. Lin, "Unique folding and hysteresis characteristics of RTD for multi-valued logic and counting applications," in 22nd ISMVL Proc., 1992.

- **J. L. Huber** received the B.S. and M.S. degrees from the University of Utah, Salt Lake City, in 1988 and 1990, respectively, and the Ph.D. degree from Yale University, New Haven, CT, in 1996. His Ph.D. thesis dealt with the physics of InAs/AlSb/GaSb resonant interband tunelling structures.

In 1996, he joined the Device and Interconnect Physics Group at Digital Semiconductor, Hudson, MA, where he has worked primarily in the area of transistor reliability due to hot-carrier effects.

**J. Chen** received the B.S. degree in materials science from Fudan University, Shanghai, P.R.O.C., in 1993. She is currently pursuing the Ph.D. degree in physics at Yale University, New Haven, CT. Her research interests include electrical properties of molecules and scanned probe lithography.

**J. A. McCormack** (S'93–M'95) was born in Hartford, CT, on July 11, 1972. He received the B.S. degree in electrical engineering from Yale University, New Haven, CT, in 1994, and the M.S. degree from Stanford University, Stanford, CA, in 1995.

Currently, he is a Hardware Design Engineer for Hewlett-Packard, Fort Collins, CO, where he is working on circuit design for the PA-8500 microprocessor.

**C. W. Zhou** was born in Hubei, China, on October 3, 1974. He received the B.S. degree from the University of Science and Technology of China, Hefei, in 1993. Currently, he is pursuing the Ph.D. degree at the Center for Microelectronic Materials and Structures, Yale University, New Haven, CT. His research interests include nanoscale fabrication, silicon micromaching, and molecular scale electronics.

M. A. Reed (SM'97) received the B.S. degree with Honors in physics, the M.S. degree in physics, and the Ph.D. degree in solid-state physics from Syracuse University, Syracuse, NY, in 1977, 1979, and 1983, respectively.

He joined Texas Instruments as a Member of the Technical Staff in the Ultrasmall Electronics Branch, where he co-founded the Nanoelectronics Research Program. In 1988, he was elected to Senior Member of the Technical Staff. In 1990, he joined the faculty at Yale Univerity, New Haven, CT, where he holds a joint appointment as Professor in the Electrical Engineering and Applied Physics Departments. Since 1995, he has been the Chairman of Electrical Engineering. His research activities have included the investigation of nanoscale and mesoscopic systems, tunneling and transport in heterojunction systems, artificially structured materials and devices, MEMS, nanotechnology, and molecular electronics. He is the author of more than 85 professional publications, has given three plenary and over 75 invited talks, and holds 11 U.S. and various foreign patents on quantum effect, heterojunction, and molecular devices. His book credits include Nanostructure Physics and Fabrication (1989), Nanostructures and Mesoscopic Systems, (1992), and Nanostructured Systems (in the series Semiconductors and Semimetals).

Dr. Reed has chaired numerous international conferences and program committees, and is an Associate Editor for a number of technical journals (such as *Physical Review Letters*). He has been elected to the Connecticut Academy of Science and Engineering, and *Who's Who in American Science and Engineering*. In October 1990, he was named by *Fortune* magazine as one of America's most promising young scientists, and in 1994 won the Kilby Young Innovator Award.