# Fabrication of fully transparent nanowire transistors for transparent and flexible electronics

SANGHYUN JU<sup>1</sup>, ANTONIO FACCHETTI<sup>2</sup>, YI XUAN<sup>1</sup>, JUN LIU<sup>2</sup>, FUMIAKI ISHIKAWA<sup>3</sup>, PEIDE YE<sup>1</sup>, CHONGWU ZHOU<sup>3</sup>. TOBIN J. MARKS<sup>2</sup>\* AND DAVID B. JANES<sup>1</sup>\*

School of Electrical and Computer Engineering, and Birck Nanotechnology Center, Purdue University, West Lafayette, Indiana 47907, USA

<sup>2</sup>Department of Chemistry and the Materials Research Center, and the Institute for Nanoelectronics and Computing, Northwestern University, Evanston, Illinois 60208-3113, USA

<sup>3</sup>Department of Electrical Engineering, University of Southern California, Los Angeles, California 90089, USA

Published online: 3 June 2007; doi:10.1038/nnano.2007.151

The development of optically transparent and mechanically flexible electronic circuitry is an essential step in the effort to develop next-generation display technologies, including 'see-through' and conformable products. Nanowire transistors (NWTs) are of particular interest for future display devices because of their high carrier mobilities compared with bulk or thin-film transistors made from the same materials, the prospect of processing at low temperatures compatible with plastic substrates, as well as their optical transparency and inherent mechanical flexibility. Here we report fully transparent  $In_2O_3$  and ZnO NWTs fabricated on both glass and flexible plastic substrates, exhibiting high-performance n-type transistor characteristics with  $\sim 82\%$  optical transparency. These NWTs should be attractive as pixel-switching and driving transistors in active-matrix organic light-emitting diode (AMOLED) displays. The transparency of the entire pixel area should significantly enhance aperture ratio efficiency in active-matrix arrays and thus substantially decrease power consumption.

In view of the inherent limitations of silicon-based electronic circuits and the demand for portable display/communication/computational/identification products, the development of high-performance transparent devices is the focus of much activity. The availability of optically transparent and mechanically flexible electronic circuitry could open the door to next-generation display technologies, including 'see-through' and conformable products.

Poly-silicon thin-film transistors (poly-Si TFTs) and amorphous-silicon thin-film transistors ( $\alpha$ -Si TFTs) are widely used to fabricate commercial displays<sup>1–3</sup>, but their lack of transparency limits their utility in transparent device applications. In this regard, recent transparent transistor research efforts have focused on enhancing transparency and flexibility while maintaining or enhancing key TFT performance metrics. There have been several recent reports of transparent transistors fabricated with ZnO, SnO<sub>2</sub>, In<sub>2</sub>O<sub>3</sub> or other semiconducting oxide thin films, or with carbon nanotube networks as the active channel layers and opaque source and drain metals, or with carbon nanotube films and transparent source/drain electrodes<sup>4–11</sup>. However, there have been no reports of fully transparent oxide nanowire transistors (NWTs) fabricated with all-transparent gate and source/drain electrodes and displaying high transistor performance.

${\rm In_2O_3}$  and ZnO nanowires are particularly promising candidates for transistor active channels satisfying these requirements because they are both transparent and mechanically robust/flexible. Furthermore, indium-tin oxide (ITO) and indium-zinc oxide (IZO) are attractive transparent conductors

for gate and source/drain electrodes<sup>12–14</sup>. In addition to transparency, transistor performance metrics such as high oncurrent  $(I_{\rm on})$ , high on/off current ratio  $(I_{\rm on}/I_{\rm off})$ , high field-effect mobility  $(\mu_{\rm eff})$ , steep subthreshold slope (S) and small threshold voltage  $(V_{\rm T})$  variation during transistor operation are required to realize commercially viable logic circuits and display devices.

Recent studies of NWTs have reported stable, high-performance transistor characteristics rivalling or surpassing those of  $\alpha$ -Si and poly-Si TFTs, especially for  $\mu_{\rm eff}$  and S (refs 15–18). The mobility observed in the present study exceeds the typical bulk mobility<sup>19</sup> reported for  ${\rm In_2O_3}$  as well as the reported mobility<sup>9</sup> in transparent  ${\rm In_2O_3}$  thin-film transistors. Similar phenomena, that is, nanowire mobilities exceeding bulk mobilities, have been reported in a number of materials 16–18. Although the exact mechanisms for this are not completely clear, the quasi-one-dimensional nature of nanowires may play a significant role in terms of reducing low-angle carrier scattering  $^{20-24}$ . The use of preformed nanowires allows low-temperature device processing, which is essential for applications such as circuits fabricated on plastic substrates.

The present results build on recent NWT studies indicating that the desired semiconductor properties can be achieved and that post-treatments such as ozone and electrical stressing further enhance device performance<sup>25</sup>. Here, we report fully transparent NWTs fabricated using all-transparent  $\rm In_2O_3$  and ZnO nanowire active channels,  $\rm Al_2O_3$  gate insulators, ITO source/drain electrodes and IZO gate electrodes. The representative  $\rm In_2O_3$

<sup>\*</sup>e-mail: t-marks@northwestern.edu; janes@ecn.purdue.edu

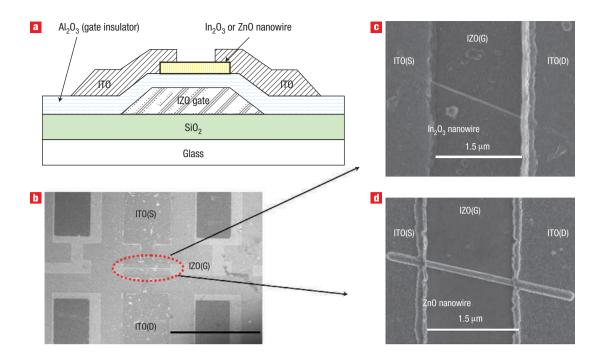

Figure 1 Fully transparent NWTs. a, Cross-sectional view of fully transparent NWT device structures consisting of a SiO $_2$  buffer layer (500 nm), patterned IZO gate electrode (120 nm), ALD-deposited Al $_2$ O $_3$  gate insulator (18 nm), a single In $_2$ O $_3$  nanowire ( $D \sim 20$  nm) or ZnO nanowire ( $D \sim 120$  nm) for the active channel, and ITO for the source/drain electrodes (120 nm). b, Top-view FE-SEM images of the devices. The IZO gate overlaps with the ITO source/drain electrodes to improve transistor performance with coverage all nanowire channel. Scale bar represents 100  $\mu$ m. c, Top-view SEM of a single In $_2$ O $_3$  nanowire region ( $D/L \sim 120$  nm/1.80  $\mu$ m). Scale bar represents 1.5  $\mu$ m. d, Top-view SEM of a single ZnO nanowire region ( $D/L \sim 120$  nm/1.66  $\mu$ m). Scale bar represents 1.5  $\mu$ m.

NWTs on glass substrates exhibit n-type transistor characteristics with  ${\sim}82\%$  visible transparency, and  $\mu_{\rm eff}$  varies from approximately 514 to  $300~{\rm cm^2\,V^{-1}\,s^{-1}}$  as the gate bias is increased from 0 V to 2 V. The representative ZnO NWTs on glass substrates exhibit  $\sim$ 83% visible transparency, with  $\mu_{\rm eff}$ varying from  $\sim$ 96 to 70 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> over the gate bias range of 0-3 V. Fully transparent and mechanically flexible In<sub>2</sub>O<sub>3</sub> NWTs with optical transmission of ~81% are also fabricated on PET plastic substrates, with  $\mu_{\rm eff} \approx 120-167~{\rm cm^2~V^{-1}~s^{-1}}$  over the reported gate bias range. We show here that the excellent transparency and semiconducting properties of In<sub>2</sub>O<sub>3</sub> and ZnO nanowires combined with Al<sub>2</sub>O<sub>3</sub> as the gate insulator, and with ITO and IZO contacts, affords high-performance NWTs that are attractive candidates for future flexible transparent display applications.

# EXPERIMENTAL RESULTS AND DISCUSSION

A cross-sectional view of the fully transparent NWT structure with an individually addressed bottom gate is shown in Fig. 1a. The structure consists of a SiO $_2$  buffer layer, a patterned IZO gate electrode, an atomic layer deposition (ALD)-derived high- $\kappa$  Al $_2$ O $_3$  gate insulator, a single-crystal semiconducting  $\rm In}_2{\rm O}_3$  (ref. 26) or ZnO (ref. 27) nanowire for the active channel, and ITO for the source/drain electrodes. No further passivation layers are used, so the dielectric above the nanowire is air. Figure 1b shows a top view of an NWT device, including all transparent components. Field-emission scanning electron microscope (FE-SEM) images of single  $\rm In}_2{\rm O}_3$  and ZnO nanowires between source and drain electrodes are shown in Fig. 1c,d, respectively. The corresponding nanowire diameters

and lengths (D/L) of single  $In_2O_3$  or ZnO nanowires addressed between source and drain on the glass substrates are  $20 \text{ nm}/1.80 \mu\text{m}$  and  $120 \text{ nm}/1.66 \mu\text{m}$ , respectively.

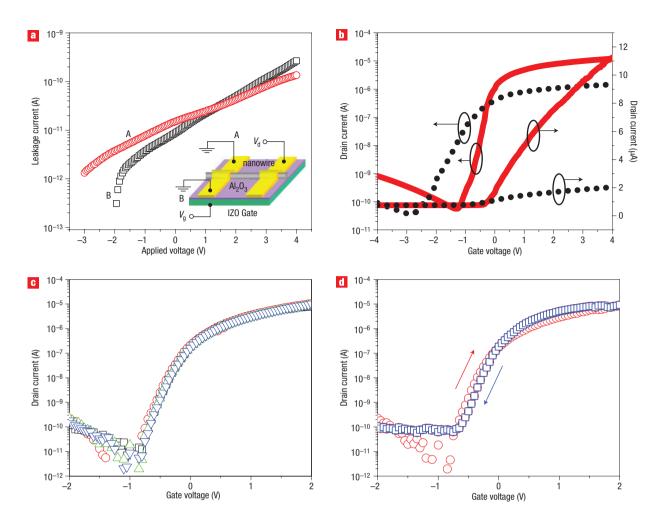

Figure 2a shows the gate and drain leakage currents of a representative In<sub>2</sub>O<sub>3</sub> NWT device for the bias configurations shown in the inset. Note that the drain leakage current here is the summation of the body current leakage of the In<sub>2</sub>O<sub>3</sub> nanowire (~40 pA at 2 V) and the leakage current through the gate dielectric ( $\sim$ 1 pA at 2 V). The  $\mathrm{Al_2O_3}$  gate dielectric exhibits excellent insulating properties, with an electrical breakdown field of > 8 MV cm<sup>-1</sup> (ref. 28) and a dielectric constant of  $\sim 9$ . The thin Al<sub>2</sub>O<sub>3</sub> gate dielectric allows the channel potential to be modulated at a relatively low gate voltage without significant gate leakage, resulting in a steep S and a high  $I_{\rm on}/I_{\rm off}$ . Figure 2b shows linear-scale and log-scale drain current versus gate-source voltage  $(I_{ds}-V_{gs})$  characteristics for the same  $In_2O_3$  NWT at  $V_d = 0.5 \text{ V}$  before 2 min of ozone treatment (black squares) and after 2 min of ozone treatment (red solid line). Ozone treatments for 2 min resulted in significant device performance enhancement in terms of S,  $V_T$  and  $I_{on}$ . Compared with asfabricated devices, S was reduced from 600 mV dec<sup>-1</sup> to 160 mV dec<sup>-1</sup>, along with improvement in  $I_{\rm on}/I_{\rm off}$  ( $\sim 1 \times 10^6$ ), and a shift in  $V_T$  from -1.16 V to -0.27 V. The improvement in S is due to change in terms of a reduction in the interfacial trap states and in fixed surface charge states<sup>25</sup>. Ozone treatment not only removes defects and contamination from the nanowire surface, but also changes the work function<sup>29,30</sup>. Ozone is also expected to increase the density of oxygen vacancies near the nanowire surface. Because oxygen vacancies act as donor states<sup>31,32</sup>, this should increase nanowire conductivity. Although the ITO and IZO microstructures and chemical bonding states

Figure 2 Characteristics of fully transparent  $In_2O_3$  NWTs. a, Gate leakage (B, black open squares) and drain leakage (A, red open circles) of the device (shown in inset). b, The linear-scale and log-scale  $I_{ds}$ – $V_{gs}$  characteristics of an  $In_2O_3$  NWT at  $V_d=0.5$  V. Arrows indicate appropriate axis. Data points are shown for the device before (black squares) and after (red solid line) 2-min ozone treatment. c, The log-scale  $I_{ds}$ – $V_{gs}$  characteristics during ten successive sweeps from -4 V to +4 V ( $V_d=0.5$  V). Black, red, green and blue data points correspond to first, second, third and fourth sweeps, respectively. The time between sweeps is  $\sim 1$  s. d, Measured  $I_{ds}$ – $V_{gs}$  characteristics showing sweeps from -2  $V_g$  (red circles) and from +2  $V_g$  to -2  $V_g$  (blue squares), as indicated by arrows ( $V_d=0.5$  V). The bias sweep rate  $(dV_g/dt)$  is 2 V s<sup>-1</sup>.

are more complex, the basic crystal structures are sufficiently similar to those of In<sub>2</sub>O<sub>3</sub> and ZnO to reasonably expect that the In<sub>2</sub>O<sub>3</sub> and ZnO nanowire work functions will increase similarly upon ozone treatment<sup>30,33</sup>. Thus, the source/drain-nanowire contact should not significantly change with ozone treatment. However, because the ozone treatment plausibly reduces nanowire surface dangling bonds and carbon contamination, and forms an oxygen vacancy-rich surface, the transistor characteristics including  $I_{\rm on}/I_{\rm off}$ , S and  $V_{\rm T}$  should be enhanced<sup>34</sup>. Figure 2c shows  $I_{\rm ds}$ – $V_{\rm gs}$  curves for another device during four successive sweeps from -2 V to +2 V, illustrating the excellent stability of the  $\rm In_2O_3$  NWT. The  $I_{\rm ds}{-}V_{\rm gs}$  curves are comparable following bias sweeps, with consistent  $I_{\text{on}}/I_{\text{off}}$ , S and  $V_{\text{T}}$  values. Furthermore, for the same device,  $I_{ds}-V_{gs}$  curves were swept from negative gate voltage  $(V_g(-))$  to positive gate voltage  $(V_{\rm g}(+))$  and back to  $V_{\rm g}(-)$  as shown in Fig. 2d. Over this bias range, the hysteresis is modest, which illustrates the excellent quality of the Al<sub>2</sub>O<sub>3</sub> gate insulator and indicates negligible charge trapping and detrapping in the gate insulator. Note that the nanowire channel active regions are not passivated in these devices.

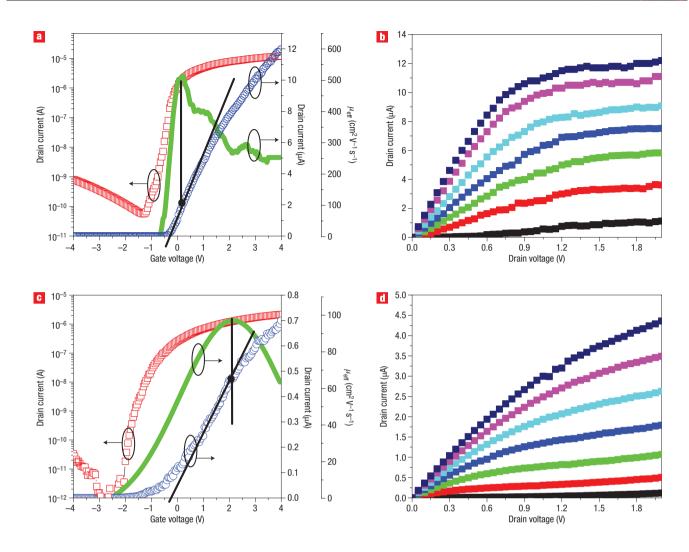

Figure 3a,c shows the  $I_{\rm ds}$ - $V_{\rm gs}$  characteristics for representative single In<sub>2</sub>O<sub>3</sub> and ZnO NWTs. The In<sub>2</sub>O<sub>3</sub> device (the same device as in Fig. 2a,b) exhibits  $S = 160 \text{ mV dec}^{-1}$ ,  $I_{\text{on}}/I_{\text{off}} = 1 \times 10^6$ and  $V_{\rm T} = -0.27$  V. The  $\mu_{\rm eff}$  of the representative  ${\rm In_2O_3}$  NWT, deduced from transconductance  $(g_{\rm m} = dI_{\rm d}/dV_{\rm g})$ , varies from  ${\sim}514$  to  $300~\text{cm}^2~\text{V}^{-1}~\text{s}^{-1}$  as the gate bias is increased from 0~Vto 2 V, following a trend that is observed in NWTs, TFTs and MOSFETs. The ZnO NWT device exhibits  $S = 0.3 \text{ V dec}^{-1}$ ,  $I_{\rm on}/I_{\rm off} \approx 1 \times 10^6$  and  $V_{\rm T} = -0.07$  V, and  $\mu_{\rm eff}$  varies from  $\sim 96$  to  $70 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  over the gate bias range of 0 V to 3 V. One important device performance metric for high-speed and lowpower operation is the  $S = dV_{gs}/dlogI_{ds}$  (mV dec<sup>-1</sup>). A small S value is required for switching transistors, ideally approaching the theoretical limit of  $\sim$ 60 mV dec<sup>-1</sup>. The present S values were extracted from the linear portion of the  $logI_{ds}$  versus  $V_{gs}$  plot (Fig. 3a,c). The very small  $\hat{S}$  values in  $In_2O_3$  and ZnO devices are comparable to other reports<sup>35,36</sup>. The drain current versus drain-source voltage  $(I_{ds}-V_{ds})$  characteristics of fully transparent single In<sub>2</sub>O<sub>3</sub> and ZnO NWTs are shown in Fig. 3b,d. These devices exhibit typical enhancement mode long-channel FET

Figure 3 Characteristics of fully transparent  $\ln_2 O_3$  and ZnO NWTs. a, The  $I_{\rm ds} - V_{\rm gs}$  characteristic of an  $\ln_2 O_3$  NWT ( $D/L \sim 20$  nm/1.80  $\mu$ m) at  $V_{\rm d} = 0.5$  V. Blue, red and green data points correspond to linear-scale  $I_{\rm ds} - V_{\rm gs}$ , log-scale  $I_{\rm ds} - V_{\rm gs}$  and  $\mu_{\rm eff}$ , respectively. Arrows indicate appropriate axis. b, The  $I_{\rm ds} - V_{\rm ds}$  characteristic of fully transparent  $\ln_2 O_3$  NWTs.  $V_{\rm g}$  ranges from -0.5 V to 2.5 V in 0.5 V steps, with the maximum current observed at  $V_{\rm g} = 2.5$  V. c, The  $I_{\rm ds} - V_{\rm gs}$  characteristic of ZnO NWTs ( $D/L \sim 120$  nm/1.66  $\mu$ m) at  $V_{\rm d} = 0.5$  V. Blue, red and green data points correspond to linear-scale  $I_{\rm ds} - V_{\rm gs}$ , log-scale  $I_{\rm ds} - V_{\rm gs}$  and  $\mu_{\rm eff}$ , respectively. Arrows indicate appropriate axis. d, The  $I_{\rm ds} - V_{\rm ds}$  characteristic of fully transparent ZnO NWTs.  $V_{\rm g}$  ranges from 0.0 V to 3.0 V in 0.5 V steps, with the maximum current observed at  $V_{\rm g} = 3.0$  V.

behaviour. For the fully transparent  $\rm In_2O_3$  single NWT device,  $I_{\rm on}$  is  $\sim 1 \times 10^{-5}~\mu \rm A$  at  $V_{\rm ds}=1.0~\rm V$  and  $V_{\rm gs}=2.0~\rm V$ . The  $I_{\rm on}$  of a ZnO single NWT device is  $\sim 2~\mu \rm A$  at  $V_{\rm ds}=1.0~\rm V$  and  $V_{\rm gs}=2.0~\rm V$ . The performance of  $\rm In_2O_3$  and ZnO NWT devices is comparable to that of previously reported non-transparent  $\rm In_2O_3$  and ZnO NWT devices  $^{35-40}$ . Because the extraction procedure for  $\mu_{\rm eff}$  involves uncertainties due to the required capacitance estimation (see Methods), NWTs can be compared with planar transistors by comparing the  $I_{\rm on}$  and  $g_{\rm m}$  per unit width  $(g_{\rm m}/W)$ , using the nanowire diameter as the device width. The  $\rm In_2O_3$  nanowire on glass exhibits an  $I_{\rm on}$  density of  $\sim \! 600~\rm mA~mm^{-1}$  and a  $g_{\rm m}/W$  of  $\sim \! 212~\rm mS~mm^{-1}$ . Both values are more than five times higher than those obtained in previous studies on transparent transistors using  $\rm In_2O_3$  thin films, even after adjusting for the differences in gate lengths and gate capacitance. The single-crystal nature of the nanowires and the formation of relatively high-quality interfaces are believed to play key roles in achieving this performance.

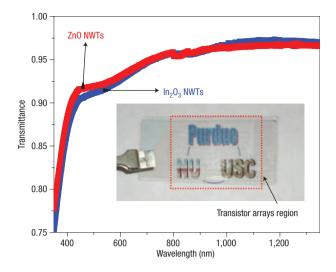

The optical transmission spectra through the  $In_2O_3$  and ZnO NWT structures, with the substrate absorption removed, are shown in Fig. 4, showing the optical transmissions to be about

90% for both transistor types. With the substrate included, the optical transmissions are  $\sim$ 82% (In<sub>2</sub>O<sub>3</sub> NWT + glass substrate) and  $\sim$ 83% (ZnO NWT + glass substrate) in the 350-1,350 nm wavelength range. The NWT array regions are  $1.0 \times 0.5$  inch (the glass substrate is 1.5 × 1.0 inch), contain 23,000 NWT device patterns, and the substrates are entirely covered by the SiO<sub>2</sub> buffer layer and the Al<sub>2</sub>O<sub>3</sub> gate insulator. The source/drain regions and the gate regions cover  $\sim$ 45% and  $\sim$ 25% of the total NWT array region, respectively. The optical absorption of the In<sub>2</sub>O<sub>3</sub> and ZnO nanowires should thus be negligible because the diameter of the nanowires is small and the area covered by the nanowires is relatively small compared with the entire NWT array. The observation of >90% optical transmission indicates that the transmission losses due to the various layers, including the nanowires, are negligible, and that visible light can readily penetrate the dense NWTs. The image in the inset of Fig. 4 shows a transparent In<sub>2</sub>O<sub>3</sub> NWT device structure, with text on an underlying opaque layer clearly visible.

Fully transparent and flexible In<sub>2</sub>O<sub>3</sub> NWT devices using a polyethylene terephthalate (PET) plastic substrate (Melinex,

**Figure 4 Optical transmission spectra through entire NWT structures.** Blue and red lines correspond to  $\ln_2 O_3$  and ZnO NWTs, respectively. The inset shows the image of a transparent  $\ln_2 O_3$  NWT substrate having 23,000 devices, showing that text on the layer behind the substrate is clearly visible.

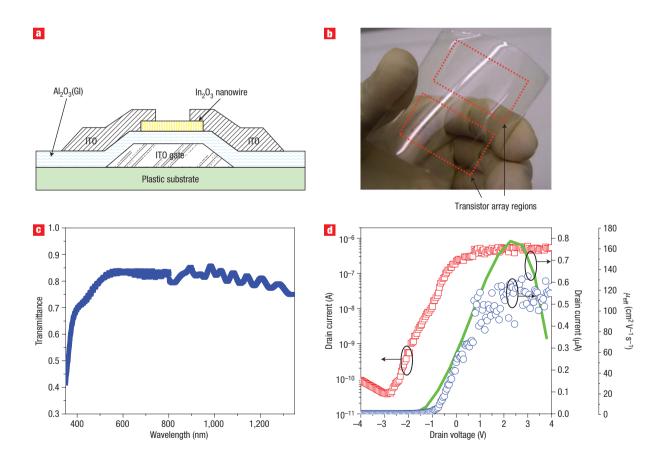

DuPont) were also fabricated. A cross-sectional view of the present fully transparent and flexible In<sub>2</sub>O<sub>3</sub> NWT device structure with an individually addressed bottom gate is shown in Fig. 5a. D and L for the single In<sub>2</sub>O<sub>3</sub> nanowires addressed between source and drain on the plastic substrate are 20 nm and 1.79 µm, respectively. In order to suppress the leakage current due to tensile/compressive stress of the plastic substrate during photolithographic processing (up to 130 °C) and gate insulator deposition (up to 200°C), a relatively thick Al<sub>2</sub>O<sub>3</sub> gate insulator (50 nm) is used. A fully transparent and flexible In<sub>2</sub>O<sub>3</sub> NWT using In<sub>2</sub>O<sub>3</sub> nanowires as the active material, ITO as the bottom gate electrodes and ITO as source/drain electrodes is shown in Fig. 5b. The optical transmission through the NWT structure and substrate, with spectra shown in Fig. 5c, is  $\sim$ 81% in the 350-1,350 nm wavelength range. Figure 5d shows the  $I_{\rm ds}$ – $V_{\rm gs}$  characteristic of a representative single In<sub>2</sub>O<sub>3</sub> NWT on the plastic substrate. Here  $S=0.9~{\rm V~dec^{-1}},~I_{\rm on}/I_{\rm off}\approx 1\times 10^5,~V_{\rm T}=-0.6~{\rm V},~{\rm and}~\mu_{\rm eff}$  varies from  $\sim 167~{\rm to}~120~{\rm cm^2~V^{-1}~s^{-1}}$  over the gate bias range of 1-3.5 V. The lower but respectable response characteristics on the plastic substrate may reflect the effects of high-temperature deposition (300 °C) and post rapid thermal annealing (500 °C for 30 s in N<sub>2</sub>). Further optimization efforts are presently in progress.

Possible applications of the present transparent NWTs include pixel drivers for AMOLED displays. For AMOLEDs, increasing the

Figure 5 Fully transparent and flexible  $\ln_2 O_3$  NWTs. **a**, Cross-sectional view of fully transparent and flexible NWT device structure consisting of a plastic substrate, patterned ITO gate electrode (120 nm), ALD-deposited  $\text{Al}_2 O_3$  gate insulator (50 nm), a single  $\ln_2 O_3$  nanowire ( $D/L \sim 20 \text{ nm}/1.79 \,\mu\text{m}$ ) for the active channel, and ITO for the source/drain electrodes (120 nm). **b**, Image of  $\ln_2 O_3$  NWTs on the plastic substrate, showing the optical clarity and mechanical flexibility. **c**, Optical transmission spectrum of region containing  $\ln_2 O_3$  NWTs on the plastic substrate (ITO(S/D)/ $\ln_2 O_3$  nanowires/ $Al_2 O_3$ /ITO(G)/plastic substrates). **d**, The  $I_{ds} - V_{gs}$  characteristic of  $\ln_2 O_3$  NWTs at  $V_d = 0.5 \text{ V}$ . Blue, red and green data points correspond to linear-scale  $I_{ds} - V_{os}$ ,  $\log$ -scale  $I_{ds} - V_{os}$  and  $\mu_{eff}$ , respectively. Arrows indicate appropriate axis.

aperture ratio is necessary to increase efficiency and reduce power consumption. For non-transparent transistors, maximizing the aperture ratio corresponds to minimizing the transistor and capacitor physical sizes. Transparent transistors would allow stacking of the drive transistors with the OLEDs, which would allow a larger transistor size (width/length) and capacitor size (single or dual capacitors). Device geometries could then be optimized to improve metrics such as peak luminescence, Commission Internationale de L'Éclairage (CIE) coordinates and power consumption. Importantly, the present NWTs exhibit relatively high performance in comparison with typical TFTs for display applications, which should allow higher operating speeds and/or smaller device areas. For instance, in order to produce white peak luminance of  $\sim 300$  cd m<sup>-2</sup> (71 × 213  $\mu$ m pixel size, 40% aperture ratio, 40% polarizer transmission, 5.1 cd A<sup>-1</sup> of red,  $13 \text{ cd A}^{-1}$  of green,  $5.7 \text{ cd A}^{-1}$  of blue, and (0.31, 0.32) of white CIE coordinates) using phosphorescent materials, driving transistors on RGB pixels must provide ~2.44 µA (red),  $\sim 1.01 \,\mu\text{A}$  (green),  $\sim 1.46 \,\mu\text{A}$  (blue) and  $\sim 3.9 \,\mu\text{A}$  (white), respectively<sup>41</sup>. Therefore, the present transparent NWTs would be suitable for switching and driving transistors on such pixels. It is also expected that the required current for AMOLED operation will decrease with increasing aperture ratio provided by alltransparent components. The realization of flexible and transparent NWTs could also enable high-resolution and lowpower consumption products such as head-up displays. Although challenges remain in the precise control of nanowire positions and orientations on large-scale substrates for NWT integration, promising advances have recently been reported<sup>42–45</sup>. For example, one report has demonstrated greater than 90% yield for the assembly of single-walled carbon nanotubes in desired positions<sup>42</sup>. Moreover, nanowire/nanotube (nanomat/nanobundles) are also possible solutions<sup>46–48</sup>. We recently reported transistors consisting of up to 22 ZnO nanowires assembled in parallel and have shown that on-current levels scale with the number of nanowires and with negligible degradation in the subthreshold slope<sup>49</sup>.

# CONCLUSIONS

In summary, fully transparent NWTs are fabricated using In<sub>2</sub>O<sub>3</sub> and ZnO nanowires as active channels, Al<sub>2</sub>O<sub>3</sub> as the gate insulator, ITO as the source/drain electrodes and IZO as the gate electrodes. The optical transmission of these devices is  $\sim$ 82%, and they exhibit transfer and current versus voltage (I-V)characteristics comparable to those observed in non-transparent devices using the same types of nanowires. Fully transparent and mechanically flexible NWTs are fabricated on plastic substrates and have an optical transmission of  $\sim$ 81%. The combination of excellent optical transparency and mechanical flexibility of In<sub>2</sub>O<sub>3</sub> and ZnO nanowires, as well as excellent device performance metrics, make these NWTs an attractive technology for realizing transparent and flexible circuits. Fully transparent NWTs will not only increase aperture ratio efficiency in active matrix arrays, but will also enable low-power consumption as well as transparency for future display technologies.

# **METHODS**

# FABRICATION OF IN2O3 AND ZNO NWT DEVICES

The 500-nm-thick  ${\rm SiO}_2$  was deposited by plasma-enhanced chemical vapour deposition on Corning 1737 glass substrates and served as a buffer and planarization layer. Individual gate electrodes were formed by sputtering IZO ( $R_{\rm sheet}=40$  ohms per square) and by ion-assisted deposition (IAD) at room temperature ( $R_{\rm sheet}=60$  ohms per square) and subsequent patterning by

photolithography and etching. An 18-nm-thick layer of Al<sub>2</sub>O<sub>3</sub> was then deposited using atomic layer deposition at 300 °C in an ASM Microchemistry F-120 ALCVD system using trimethyl aluminium (Al(CH<sub>3</sub>)<sub>3</sub>) (TMA) and water as precursors. Following Al<sub>2</sub>O<sub>3</sub> deposition, the substrates were annealed at 500 °C for 30 s under N<sub>2</sub> to improve the film quality. Next, a suspension of In<sub>2</sub>O<sub>2</sub> or ZnO nanowires in VLSI-grade 2-propanol solution was disbursed on the gate patterned substrates. Single-crystal semiconducting In<sub>2</sub>O<sub>3</sub> nanowires were synthesized by a pulsed laser ablation process<sup>26</sup>, with average diameter and length of 20 nm and 5 µm, respectively. Powdered ZnO nanowires synthesized by thermal evaporation and condensation were purchased from Nanolab. The average diameter and length were 120 nm and 5 µm, respectively, and microstructural characterization indicated that they were highly crystalline<sup>27</sup>. Finally, ITO source/drain electrodes were deposited by IAD at room temperature and patterned by photolithography. Following source/drain electrode patterning, the NWTs were subjected to an ozone treatment (UV-Ozone cleaner, UVO 42-220, Jelight) for 2 min to achieve optimum transistor performance in terms of  $I_{on}$ ,  $I_{on}$ : $I_{off}$  ratio, S and  $\mu_{eff}$ . The ozone environment was obtained by setting the oxygen content to 50 p.p.m., the ultraviolet (UV) wavelength to 184.9 nm and UV lamp power to 28 mW cm<sup>-2</sup> at 254 nm. Note that the devices were shielded from UV light. Fully transparent and flexible In2O3 NWT devices using PET (Melinex, DuPont) were also fabricated with a PET/ITO(G)/Al<sub>2</sub>O<sub>3</sub>/In<sub>2</sub>O<sub>3</sub> nanowire/ITO(S/D) structure (Fig. 5a). The 50-nm-thick Al<sub>2</sub>O<sub>3</sub> layer was deposited at 200 °C. The ITO for the gate and source/drain electrodes was deposited using IAD. The nanowire lengths of given transistors between source and drain were obtained from the FE-SEM image, and account for the angle between the nanowire and the electrode edges.

### CHARACTERIZATION METHODOLOGY

The work function of an as-grown ITO thin film was measured using an AC-2, RKI Instruments photoelectron spectrometer. The UV-Vis spectra were recorded with a Varian Cary 1E spectrophotometer. Electrical  $I\!-\!V$  measurements were performed using a Keithley 4200 semiconductor characterization system. The nanowires within a device were imaged with a Hitachi S-4800 FE-SEM following electrical characterization.

# CALCULATION OF MOBILITY AND THRESHOLD VOLTAGE

In contrast with planar transistors in which carrier concentration and mobility can be determined independently, for example, through Hall effect and conductivity measurements, the lack of extended lateral geometries in NWTs dictates an alternative approach for determining mobility. Following the typical approach used in earlier NWT studies, we calculated a field-effect mobility ( $\mu_{\rm eff}$ ) using a combination of the cylinder-on-plate (COP) capacitance model  $C_i = 2\pi\epsilon_0 k_{\rm eff} L/\cosh^{-1}(1+t_{\rm ox}/r)$  and the relationship  $\mu = \mathrm{d}I_\mathrm{ds}/\mathrm{d}V_\mathrm{gs} \times L^2/C_i \times 1/V_\mathrm{ds}$  obtained from the MOSFET linear region model<sup>50</sup>, where a  $k_{\rm eff}$  value of  $\sim$ 9.0 is the effective dielectric constant of Al<sub>2</sub>O<sub>3</sub>, L is the channel length of the NWTs ( $\sim$ 1.80  $\mu$ m for an In<sub>2</sub>O<sub>3</sub> nanowire,  $\sim$ 1.66 µm for a ZnO nanowire), r is the radius of the NWTs (10 nm for the  $In_2O_3$  nanowire, 60 nm for the ZnO nanowire),  $t_{ox} \sim 18$  nm is the thickness of the gate insulator,  ${\rm d}I_{\rm ds}/{\rm d}V_{\rm gs}$  is the transconductance and  $V_{\rm ds}$  is drain voltage. In the case of flexible and transparent  $In_2O_3$  NWTs,  $L \sim 1.79 \mu m$  and  $r \sim 10 nm$ are used. Our device geometry consists of the gate dielectric ( $k_{\rm eff} \sim 9)$  below and air  $(k_{\rm eff}\sim 1)$  above the nanowire. A previous comparision  $^{51}$  between electrostatic simulations and an analytic formula for capacitance (a form of the COP equation valid for  $t_{\rm ox} \gg r$ ) for a comparable geometry to  ${\rm SiO_2/air}$  showed good agreement between the two capacitances over a range of  $t_{ox}/r$  from 8 to 40, provided that a value of  $k_{\rm eff} = 0.5 \epsilon_{\rm R1SiO2}$  was used. As our geometry uses a higher k dielectric constant and smaller  $t_{\rm ox}/r$  ( $\sim$ 1.8), the fringing fields are more tightly confined to the gate dielectric layer. We have therefore chosen to use  $k_{\rm eff} \sim \varepsilon_{\rm R1A12O3}$ , which would tend to overestimate the capacitance (because the appropriate correction factor is greater than 0.5 but less than 1.0), and therefore underestimate the mobility. The transconductances shown in Fig. 3a,b and Fig. 4d have been smoothed by polynomial fit to three orders with 20 points fit to the curve. In order to extract  $V_{\rm T}$  here we used the extrapolated  $V_{\rm T}$  (  $V_{\rm T}=$  $V_{\rm G}(g_{\rm m\_max}) - (I_{\rm D}(g_{\rm m\_max})/g_{\rm m\_max}) \text{ where } g_{\rm m} = \partial I_{\rm D}/\partial V_{\rm G} \text{ (at } V_{\rm d} = 0.5 \text{ V)),}$ because it gives an accurate  $V_{\mathrm{T}}$  The gate voltage at the maximum  $g_{\rm m}(V_{\rm g}(g_{

m m\_max}))$ , the drain current at the maximum  $g_{

m m}$ ,  $I_{

m d}(g_{

m m\_max})$ , and the maximum  $g_{\rm m}(g_{\rm m\_max})$  are obtained from Fig. 3a,c and Fig. 5d. These values are confirmed with  $V_{\rm T}$  values obtained from the  $I_{\rm ds}$ - $V_{\rm ds}$ curve at  $V_d = 0.1 \text{ V}$ .

Received 2 January 2007; accepted 26 April 2007; published 3 June 2007.

### References

- 1. Snell, A. J., Mackenzie, K. D., Spear, W. E., LeComber, P. G. & Hughes, A. J. Application of amorphous silicon field effect transistors in addressable liquid crystal display panels. Appl. Phys. Lett. **24,** 357–362 (1981).

- Madelung, O. (ed.) Technology and Applications of Amorphous Silicon (Springer, Berlin, 2000).

- Ucjikoga, S. Low-temperature polycrystalline silicon thin-film transistor technologies for systemonglass displays. MRS Bull. 27, 881-886 (2002).

- Carcia, P. F., McLean, R. S., Reilly, M. H. & Nunes, G. Transparent ZnO thin-film transistor fabricated by rf magnetron sputtering. Appl. Phys. Lett. 82, 1117-1119 (2003).

- Fortunato, E.et al. Recent advances in ZnO transparent thin film transistors. Thin Solid Films 487, 205-211 (2005).

- Hoffman, R. L., Norris, B. J. & Wager, J. F. ZnO-based transparent thin-film transistors. Appl. Phys. Lett. 82, 733-735 (2003).

- Nomura, K. et al. Thin-film transistor fabricated in single-crystalline transparent oxide semiconductor. Science 300, 1269-1272 (2003).

- Presley, R. E. et al. Tin oxide transparent thin-film transistors. J. Phys. D. 37, 2810-2813 (2004).

- Wang, L. et al. High performance all transparent inorganic-organic hybrid thin-film transistors. Nature Mater. 5, 893-900 (2006).

- 10. Hur, S.-H. Park, O. & Rogers, J.A. Extreme bendability of single-walled carbon nanotube networks transferred from high-temperature growth substrates to plastic and their use in thin-film transistors. Appl. Phys. Lett. 86, 243502 (2005).

- 11. Takenobu, T. *et al.* High-performance transparent flexible transistors using carbon nanotube films. Appl. Phy. Lett. 88, 33511 (2006).

- 12. Minami, T., Yamamoto, T., Toda, Y. & Miyata, T. Transparent conducting zinc-co-doped ITO films

- prepared by magnetron sputtering. *Thin Solid Films* **373**, 189–194 (2000).

13. Yaglioglu, B., Yeom, H.-Y. & Paine, D. C. Crystallization of amorphous In<sub>2</sub>O<sub>3</sub>-10 wt% ZnO thin films annealed in air. Appl. Phy. Lett. 86, 261908 (2005).

- 14. Fortunato, E. et al. High mobility amorphous/nanocrystalline indium zinc oxide deposited at room temperature. Thin Solid Films 502, 104-107 (2006).

- 15. Xiang, J. et al. Ge/Si nanowire heterostructures as high-performance field-effect transistors. Nature **441,** 489–493 (2006).

- 16. Cui, Y., Zhong, Z., Wang, D., Wang, W. U. & Lieber, C. M. High performance silicon nanowire field effect transistors. Nano Lett. 3, 149-152 (2003).

- 17. Cha, S. N. et al. High performance ZnO nanowire field effect transistor. Proc. ESSDERC 217-220 (2005).

- 18. Kim, W. et al. Germanium nanowire field-effect transistors with SiO<sub>2</sub> and high-κ HfO<sub>2</sub> gate dielectrics. Appl. Phys. Lett. 87, 173101 (2005).

- 19. Weiher, R. L. Electrical properties of single crystals of indium oxide. J. Appl. Phys. 33, 2834-2839 (1962).

- 20. Li, Y., Meng, G. W., Zhang, L. D. & Phillipp, F. Ordered semiconductor ZnO nanowire arrays and their photoluminescence properties. Appl. Phys. Lett. 76, 2011-2013 (2000).

- 21. Yao, B. D., Chan, Y. F. & Wang, N. Formation of ZnO nanostructures by a simple way of thermal evaporation. Appl. Phys. Lett. 81, 757-759 (2002).

- 22. Banerjee, D. et al. Large-quantity free-standing ZnO nanowires. Appl. Phys. Lett. 83, 2061-2063 (2003).

- 23. Pan, Z. W., Dai, Z. R. & Wang, Z. L. Nanobelts of semiconducting oxides. Science 291, 1947-1949 (2001).

- 24. Wan, Q., Yu, K., Wang, T. H. & Lin, C. L. Low-field electron emission from tetrapod-like ZnO nanostructures synthesized by rapid evaporation. *Appl. Phys. Lett.* **83**, 2253–2255 (2003). 25. Ju, S., Janes, D. B., Lu, G., Facchetti, A. & Marks, T. J. Effects of bias stress on ZnO nanowire

- field-effect transistors fabricated with organic gate nanodielectrics. Appl. Phys. Lett. 89, 193506 (2006).

- 26. Li, C. et al. Diameter-controlled growth of single-crystalline  $\rm In_2O_3$  nanowires and their electronic properties. Adv. Mater. 15, 143-145 (2003).

- 27. Banerjee, D. et al. Synthesis and photoluminescence studies on ZnO nanowires. Nanotechnology 15. 404-409 (2004).

- 28. Lin, H. C., Ye, P. D. & Wilk, G. D. Leakage current and breakdown electric-field studies on ultrathin atomic-layer-deposited Al<sub>2</sub>O<sub>3</sub> on GaAs. Appl. Phys. Lett. 87, 182904 (2005).

- 29. Lang, O. et al. Thin film growth and band lineup of In2O3 on the layered semiconductor InSe. J. Appl. Phys. 86, 5687-5691 (1999).

- 30. Gassenbauer, Y. et al. Surface states, surface potentials, and segregation at surfaces of tin-doped In2O3. Phys. Rev. B 73, 245312 (2006).

- 31. Goldberger, J., Sirbuly, D., Law, M. & Yang, P. ZnO nanowire transistors. J. Phys. Chem. B 109, 9-14 (2005).

- 32. Martins, R. et al. Zinc oxide as an ozone sensor. J. Appl. Phys. 96, 1398–1408 (2004).

33. Jiang, X., Wong, F. L., Fung, M. K. & Lee, S. T. Aluminum-doped zinc oxide films as transparent conductive electrode for organic light-emitting devices. Appl. Phys. Lett. 83, 1875–1877 (2003).

- 34. Kim, S. Y., Lee, J.-L., Kim, K.-B. & Tak, Y.-H. Effect of ultraviolet-ozone treatment of indium-tin-

- oxide on electrical properties of organic light emitting diodes. *J. Appl. Phys.* **95**, 2560–2563 (2004). 35. Liu, F. *et al.* One-dimensional transport of In<sub>2</sub>O<sub>3</sub> nanowires. *Appl. Phys. Lett.* **86**, 213101 (2005).

- 36. Chang, P.-C. et al. High-performance ZnO nanowire field effect transistors. Appl. Phys. Lett. 89, 133113 (2006).

- 37. Zhang, D. et al. Electronic transport studies of single-crystalline In2O3 nanowires. Appl. Phys. Lett. 82, 112-114 (2003)

- 38. Cha, S. N. et al. High-performance ZnO nanowire field effect transistor using self-aligned nanogap gate electrodes. Appl. Phys. Lett. 89, 263102 (2006)

- 39. Moon, T.-H. et al. Chemical surface passivation of HfO<sub>2</sub> films in a ZnO nanowire transistor. Nanotechnology 17, 2116-2121 (2006).

- 40. Ju, S. et al. Low operating voltage single ZnO nanowire field-effect transistors enabled by self-assembled organic gate nanodielectrics. Nano Lett. 5, 2281-2286 (2005).

- 41. Ju, S. H. et al. High performance 2.2" QCIF full color AMOLED displays based on electrophosphorescence. SID 02 DIGEST 37.3, 1096-1099 (2002).

- 42. Rao, S., Huang, L., Setyawan, W. & Hong, S. Nanotube electronics: Large-scale assembly of carbon nanotubes. Nature 425, 36-37 (2003).

- 43. Wu, Y., Xiang, J., Yang, C., Lu, W. & Lieber, C. M. Single-crystal metallic nanowires and metal/semiconductor nanowire heterostructures. Nature 430, 61-65 (2004)

- Joseph, V. R. et al. Electronic connection to the interior of a mesoporous insulator with nanowires of crystalline RuO<sub>2</sub>. Nature 406, 169–172 (2000).

- 45. Huang, Y., Duan, X., Wei, Q. & Lieber, C. M. Directed assembly of one-dimensional nanostructures into functional networks. Science 291, 630-633 (2001). 46. Kuykendall, T. et al. Crystallographic alignment of high-density gallium nitride nanowire arrays.

- Nature Mater. 3, 524-528 (2004).

- 47. Duan, X. et al. High-performance thin-film transistors using semiconductor nanowires and nanoribbons. Nature 425, 274-278 (2003).

- 48. Menard, E., Lee, K. J., Khang, D. Y., Nuzzo, R. G. & Rogers, J. A. A printable form of silicon for high performance thin film transistors on plastic substrates. Appl. Phys. Lett. 84, 5398-5400 (2004).

- 49. Ju, S. et al. n-Type field-effect transistors using multiple Mg-doped ZnO nanorods. IEEE Trans. Nanotech. (in the press).

- 50. Wang, D. et al. Germanium nanowire field-effect transistors with  $SiO_2$  and high- $\kappa$  HfO $_2$  gate dielectrics. Appl. Phys. Lett. 83, 2432-2434 (2003).

- 51. Vashaee, D. et al. Electrostatics of nanowire transistors with triangular cross sections. J. Appl. Phys. 99, 54310 (2006).

### Acknowledgements

We thank Samsung SDI for providing substrate materials and measuring the ITO work function. This work was supported in part by the NASA Institute for Nanoelectronics and Computing under grant NCC-2-1363 and the Northwestern University MRSEC under grant DMR-0520513. Correspondence and requests for materials should be addressed to T.J.M. and D.B.J.

# **Author contributions**

All authors contributed equally to this work and all discussed the results and commented on

# Competing financial interests

The authors declare no competing financial interests.

Reprints and permission information is available online at http://npg.nature.com/reprintsandpermissions/